- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄4214 > XCV405E-7FG676I (Xilinx Inc)IC FPGA 1.8V 676-BGA PDF資料下載

參數(shù)資料

| 型號(hào): | XCV405E-7FG676I |

| 廠商: | Xilinx Inc |

| 文件頁(yè)數(shù): | 22/118頁(yè) |

| 文件大?。?/td> | 0K |

| 描述: | IC FPGA 1.8V 676-BGA |

| 產(chǎn)品變化通告: | FPGA Family Discontinuation 18/Apr/2011 |

| 標(biāo)準(zhǔn)包裝: | 1 |

| 系列: | Virtex®-E EM |

| LAB/CLB數(shù): | 2400 |

| 邏輯元件/單元數(shù): | 10800 |

| RAM 位總計(jì): | 573440 |

| 輸入/輸出數(shù): | 404 |

| 門數(shù): | 129600 |

| 電源電壓: | 1.71 V ~ 1.89 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | -40°C ~ 100°C |

| 封裝/外殼: | 676-BGA |

| 供應(yīng)商設(shè)備封裝: | 676-FBGA(27x27) |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)當(dāng)前第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)

Virtex-E 1.8 V Extended Memory Field Programmable Gate Arrays

Module 4 of 4

DS025-4 (v3.0) March 21, 2014

42

R

— OBSOLETE — OBSOLETE — OBSOLETE — OBSOLETE —

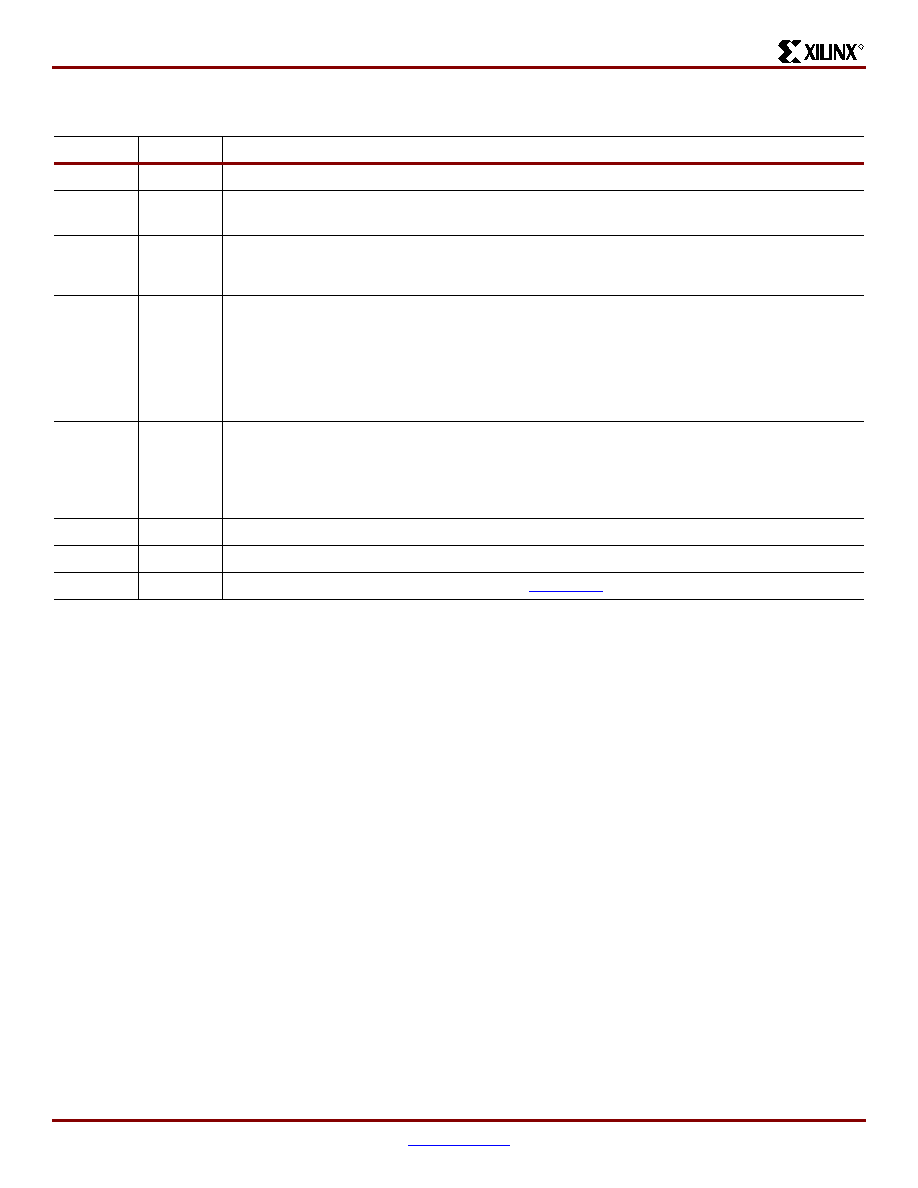

Revision History

The following table shows the revision history for this document.

Virtex-E Extended Memory Data Sheet

The Virtex-E Extended Memory Data Sheet contains the following modules:

DS025-1, Virtex-E 1.8V Extended Memory FPGAs:

Introduction and Ordering Information (Module 1)

DS025-2, Virtex-E 1.8V Extended Memory FPGAs:

Functional Description (Module 2)

DS025-3, Virtex-E 1.8V Extended Memory FPGAs:

DC and Switching Characteristics (Module 3)

DS025-4, Virtex-E 1.8V Extended Memory FPGAs:

Pinout Tables (Module 4)

Date

Version

Revision

03/23/2000

1.0

Initial Xilinx release.

08/01/2000

1.1

Accumulated edits and fixes. Upgrade to Preliminary. Preview -8 numbers added. Reformatted

to adhere to corporate documentation style guidelines. Minor changes in BG560 pin-out table.

09/19/2000

1.2

In Table 3 (Module 4), FG676 Fine-Pitch BGA — XCV405E, the following pins are no longer

labeled as VREF: B7, G16, G26, W26, AF20, AF8, Y1, H1.

Min values added to Virtex-E Electrical Characteristics tables.

11/20/2000

1.3

Updated speed grade -8 numbers in Virtex-E Electrical Characteristics tables (Module 3).

Updated minimums in Table 11 (Module 2), and added notes to Table 12 (Module 2).

Added to note 2 of Absolute Maximum Ratings (Module 3).

Changed all minimum hold times to –0.4 for Global Clock Set-Up and Hold for LVTTL

Standard, with DLL (Module 3).

Revised maximum TDLLPW in -6 speed grade for DLL Timing Parameters (Module 3).

04/02/2001

1.4

In Table 4, FG676 Fine-Pitch BGA — XCV405E, pin B19 is no longer labeled as VREF, and

pin G16 is now labeled as VREF.

Updated values in Virtex-E Switching Characteristics tables.

Converted data sheet to modularized format. See the Virtex-E Extended Memory Data

Sheet section.

07/23/2001

1.5

Changed definition of T31 and T32 pins in Table 1 for XCV405E and the XCV812E devices.

07/17/2002

1.6

Data sheet designation upgraded from Preliminary to Production.

03/21/2014

3.0

This product is obsolete/discontinued per XCN12026.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XC6VLX195T-1FFG784C | IC FPGA VIRTEX 6 199K 784FFGBGA |

| XC6VCX130T-2FFG784I | IC FPGA VIRTEX 6 128K 784FFGBGA |

| XC4VLX60-11FF668I | IC FPGA VIRTEX-4LX 668FFBGA |

| XC4VLX60-12FFG668C | IC FPGA VIRTEX-4 LX 60K 668FCBGA |

| XC4VLX60-11FFG668I | IC FPGA VIRTEX-4 LX 60K 668FCBGA |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XCV405E-7FG900C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Virtex-E 1.8 V Extended Memory Field Programmable Gate Arrays |

| XCV405E-7FG900I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Virtex-E 1.8 V Extended Memory Field Programmable Gate Arrays |

| XCV405E-8BG404C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Virtex-E 1.8 V Extended Memory Field Programmable Gate Arrays |

| XCV405E-8BG404I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Virtex-E 1.8 V Extended Memory Field Programmable Gate Arrays |

| XCV405E-8BG556C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Virtex-E 1.8 V Extended Memory Field Programmable Gate Arrays |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。