- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄4269 > XC3S1200E-4FGG400I (Xilinx Inc)IC FPGA SPARTAN-3E 1200K 400FBGA PDF資料下載

參數(shù)資料

| 型號(hào): | XC3S1200E-4FGG400I |

| 廠商: | Xilinx Inc |

| 文件頁數(shù): | 18/227頁 |

| 文件大?。?/td> | 0K |

| 描述: | IC FPGA SPARTAN-3E 1200K 400FBGA |

| 標(biāo)準(zhǔn)包裝: | 60 |

| 系列: | Spartan®-3E |

| LAB/CLB數(shù): | 2168 |

| 邏輯元件/單元數(shù): | 19512 |

| RAM 位總計(jì): | 516096 |

| 輸入/輸出數(shù): | 304 |

| 門數(shù): | 1200000 |

| 電源電壓: | 1.14 V ~ 1.26 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | -40°C ~ 100°C |

| 封裝/外殼: | 400-BGA |

| 供應(yīng)商設(shè)備封裝: | 400-FBGA(21x21) |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁當(dāng)前第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁第162頁第163頁第164頁第165頁第166頁第167頁第168頁第169頁第170頁第171頁第172頁第173頁第174頁第175頁第176頁第177頁第178頁第179頁第180頁第181頁第182頁第183頁第184頁第185頁第186頁第187頁第188頁第189頁第190頁第191頁第192頁第193頁第194頁第195頁第196頁第197頁第198頁第199頁第200頁第201頁第202頁第203頁第204頁第205頁第206頁第207頁第208頁第209頁第210頁第211頁第212頁第213頁第214頁第215頁第216頁第217頁第218頁第219頁第220頁第221頁第222頁第223頁第224頁第225頁第226頁第227頁

Spartan-3E FPGA Family: Functional Description

DS312 (v4.1) July 19, 2013

Product Specification

114

Notice of Disclaimer

THE XILINX HARDWARE FPGA AND CPLD DEVICES REFERRED TO HEREIN (“PRODUCTS”) ARE SUBJECT TO THE TERMS AND

CONDITIONS OF THE XILINX LIMITED WARRANTY WHICH CAN BE VIEWED AT http://www.xilinx.com/warranty.htm. THIS LIMITED

WARRANTY DOES NOT EXTEND TO ANY USE OF PRODUCTS IN AN APPLICATION OR ENVIRONMENT THAT IS NOT WITHIN THE

SPECIFICATIONS STATED IN THE XILINX DATA SHEET. ALL SPECIFICATIONS ARE SUBJECT TO CHANGE WITHOUT NOTICE.

PRODUCTS ARE NOT DESIGNED OR INTENDED TO BE FAIL-SAFE OR FOR USE IN ANY APPLICATION REQUIRING FAIL-SAFE

PERFORMANCE, SUCH AS LIFE-SUPPORT OR SAFETY DEVICES OR SYSTEMS, OR ANY OTHER APPLICATION THAT INVOKES

THE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR PROPERTY OR ENVIRONMENTAL DAMAGE (“CRITICAL

APPLICATIONS”). USE OF PRODUCTS IN CRITICAL APPLICATIONS IS AT THE SOLE RISK OF CUSTOMER, SUBJECT TO

APPLICABLE LAWS AND REGULATIONS.

CRITICAL APPLICATIONS DISCLAIMER

XILINX PRODUCTS (INCLUDING HARDWARE, SOFTWARE AND/OR IP CORES) ARE NOT DESIGNED OR INTENDED TO BE

FAIL-SAFE, OR FOR USE IN ANY APPLICATION REQUIRING FAIL-SAFE PERFORMANCE, SUCH AS IN LIFE-SUPPORT OR

SAFETY DEVICES OR SYSTEMS, CLASS III MEDICAL DEVICES, NUCLEAR FACILITIES, APPLICATIONS RELATED TO THE

DEPLOYMENT OF AIRBAGS, OR ANY OTHER APPLICATIONS THAT COULD LEAD TO DEATH, PERSONAL INJURY OR SEVERE

PROPERTY OR ENVIRONMENTAL DAMAGE (INDIVIDUALLY AND COLLECTIVELY, “CRITICAL APPLICATIONS”). FURTHERMORE,

XILINX PRODUCTS ARE NOT DESIGNED OR INTENDED FOR USE IN ANY APPLICATIONS THAT AFFECT CONTROL OF A

VEHICLE OR AIRCRAFT, UNLESS THERE IS A FAIL-SAFE OR REDUNDANCY FEATURE (WHICH DOES NOT INCLUDE USE OF

SOFTWARE IN THE XILINX DEVICE TO IMPLEMENT THE REDUNDANCY) AND A WARNING SIGNAL UPON FAILURE TO THE

OPERATOR. CUSTOMER AGREES, PRIOR TO USING OR DISTRIBUTING ANY SYSTEMS THAT INCORPORATE XILINX

PRODUCTS, TO THOROUGHLY TEST THE SAME FOR SAFETY PURPOSES. TO THE MAXIMUM EXTENT PERMITTED BY

APPLICABLE LAW, CUSTOMER ASSUMES THE SOLE RISK AND LIABILITY OF ANY USE OF XILINX PRODUCTS IN CRITICAL

APPLICATIONS.

AUTOMOTIVE APPLICATIONS DISCLAIMER

XILINX PRODUCTS ARE NOT DESIGNED OR INTENDED TO BE FAIL-SAFE, OR FOR USE IN ANY APPLICATION REQUIRING

FAIL-SAFE PERFORMANCE, SUCH AS APPLICATIONS RELATED TO: (I) THE DEPLOYMENT OF AIRBAGS, (II) CONTROL OF A

VEHICLE, UNLESS THERE IS A FAIL-SAFE OR REDUNDANCY FEATURE (WHICH DOES NOT INCLUDE USE OF SOFTWARE IN

THE XILINX DEVICE TO IMPLEMENT THE REDUNDANCY) AND A WARNING SIGNAL UPON FAILURE TO THE OPERATOR, OR (III)

USES THAT COULD LEAD TO DEATH OR PERSONAL INJURY. CUSTOMER ASSUMES THE SOLE RISK AND LIABILITY OF ANY

USE OF XILINX PRODUCTS IN SUCH APPLICATIONS.

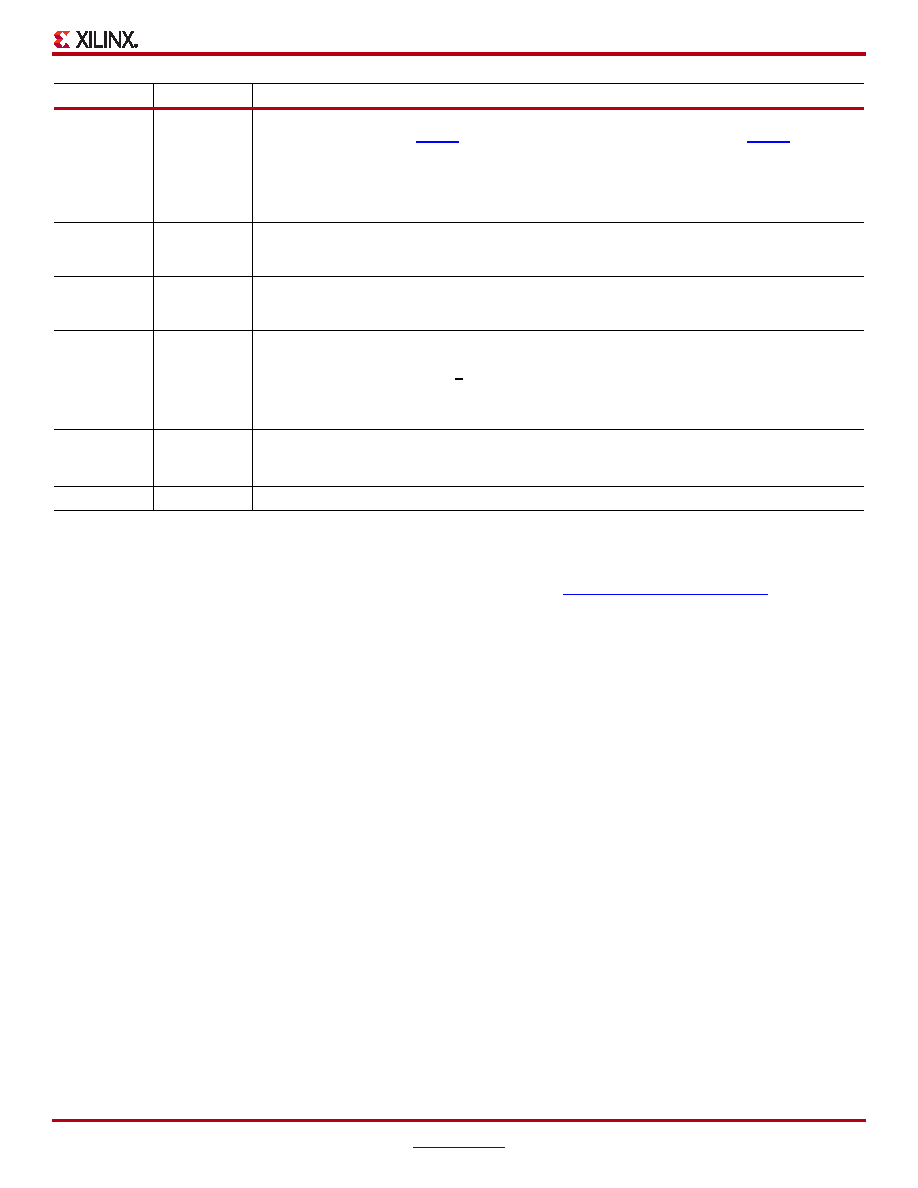

03/16/2007

3.5

Added information about new Spartan-3 Generation user guides (Design Documentation Available).

Generation Configuration User Guide. Added note about possible JTAG configuration issues when the

FPGA mode pins are set for Master mode and using software prior to ISE 9.1.01i (JTAG Mode).

Removed a few lingering references to “weak” pull-up resistors, including in Figure 12. Removed

vestigial references regarding the LDC[2:0] and HDC pins during Slave Parallel Mode configuration.

These pins are not used in this configuration mode.

05/29/2007

3.6

Added information about HSWAP and PCI differences between steppings to Table 71. Removed

“Performance Differences between Global Buffers” to match improved specs in Module 3. Updated

PROG_B pulse width descriptions to match specification in Module 3.

04/18/2008

3.7

Corrected Figure 6 to show six taps and updated associated text. Added note for recommended pull-up

on DONE in Table 55 and elsewhere. Added a caution regarding Persist of pins A20-A23. Updated

Stepping description in Table 71 to note that only Stepping 1 is in production today. Updated links.

08/26/2009

3.8

Added a frequency limitation to Equation 6. Added a new Equation 7 with a frequency limitation. Added

a Spread Spectrum, page 57 paragraph. Added Table 42, page 61. Updated a Flash vendor name in

Table 61, page 89. Removed the < symbol from the flash read access times in Table 62, page 89.

Revised the first paragraph in Configuration Sequence, page 102. Revised the first paragraph in

Power-On Behavior, page 111. Revised the second paragraph in Production Stepping, page 112.

Revised the first paragraph in Ordering a Later Stepping, page 112.

10/29/2012

4.0

Added Notice of Disclaimer. This product is not recommended for new designs.

Updated the design note section in VARIABLE Phase Shift Mode. Added the VQ100 to the Quadrant

Clock Routing section.

07/19/2013

4.1

Removed banner. This product IS recommended for new designs.

Date

Version

Revision

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| GSC43DTEI | CONN EDGECARD 86POS .100 EYELET |

| XC6SLX25T-N3FGG484I | IC FPGA SPARTAN-6 484FBGA |

| XC3S1000-4FGG456I | SPARTAN-3A FPGA 1M STD 456-FBGA |

| XC3S1000-5FGG456C | SPARTAN-3A FPGA 1M 456-FBGA |

| GEC50DTEI | CONN EDGECARD 100POS .100 EYELET |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XC3S1200E-4FGG484C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan-3E FPGA Family |

| XC3S1200E-4FGG484I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan-3E FPGA Family |

| XC3S1200E-4FT256C | 制造商:Xilinx 功能描述:FPGA SPARTAN-3E 1.2M GATES 19512 CELLS 572MHZ 90NM 1.2V 256F - Trays |

| XC3S1200E-4FT256CES | 制造商:Xilinx 功能描述: |

| XC3S1200E-4FT256I | 功能描述:IC FPGA SPARTAN 3E 256FTBGA RoHS:否 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:Spartan®-3E 標(biāo)準(zhǔn)包裝:40 系列:Spartan® 6 LX LAB/CLB數(shù):3411 邏輯元件/單元數(shù):43661 RAM 位總計(jì):2138112 輸入/輸出數(shù):358 門數(shù):- 電源電壓:1.14 V ~ 1.26 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 100°C 封裝/外殼:676-BGA 供應(yīng)商設(shè)備封裝:676-FBGA(27x27) |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。