- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄199495 > TSPC860SRMZPU50D4 (E2V TECHNOLOGIES PLC) 32-BIT, 50 MHz, RISC PROCESSOR, PBGA357 PDF資料下載

參數(shù)資料

| 型號(hào): | TSPC860SRMZPU50D4 |

| 廠商: | E2V TECHNOLOGIES PLC |

| 元件分類(lèi): | 微控制器/微處理器 |

| 英文描述: | 32-BIT, 50 MHz, RISC PROCESSOR, PBGA357 |

| 封裝: | PLASTIC, BGA-357 |

| 文件頁(yè)數(shù): | 35/90頁(yè) |

| 文件大小: | 2351K |

| 代理商: | TSPC860SRMZPU50D4 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)當(dāng)前第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)

40

TSPC860

2129A–HIREL–08/02

Notes:

1. Phase and frequency jitter performance results are only valid if the input jitter is less than the prescribed value.

2. If the rate of change of the frequency of EXTAL is slow (i.e. it does not jump between the minimum and maximum values in

one cycle) or the frequency of the jitter is fast (i.e. it does not stay at an extreme value for a long time) then the maximum

allowed jitter on EXTAL can be up to 2%

3. The timings specified in B4 and B5 are based on full strength clock.

4. The timing for BR output is relevant when the PC860 is selected to work with the external bus arbiter. The timing for BG out-

put is relevant when the PC860 is selected to work with internal bus arbiter.

5. The timing required for BR input is relevant when the TSPC860 is selected to work with internal bus arbiter. The timing for

BG input is relevant when the TSPC860 is selected to work with internal bus arbiter.

6. The D (0:31) and DP (0:3) input timings B20 and B21 refer to the rising edge of the CLKOUT in which the TA input signal is

asserted.

7. The D (0:31) and DP (0:3) input timings B20 and B21 refer to the falling edge of the CLKOUT. This timing is valid only for

read accesses controlled by chip-selects under control of the UPM in the Memory Controller, for data beats where DLT3 = 1

in the UPM RAM words. (This is only the cases where data is latched on the falling edge of CLKOUT).

8. The timing B30 refers to CS when ACS = 00 and to WE (0:3) when CSNT = 0

9. The signal UPWAIT is considered asynchronous to the CLKOUT and synchronized internally. The timings specified in B37

and B38 are specified to enable the freeze of the UPM output signals as described in Figure 22.

10. The AS signal is considered asynchronous to the CLKOUT. The timing B39 is specified in order to allow the behavior speci-

fied in Figure 25.

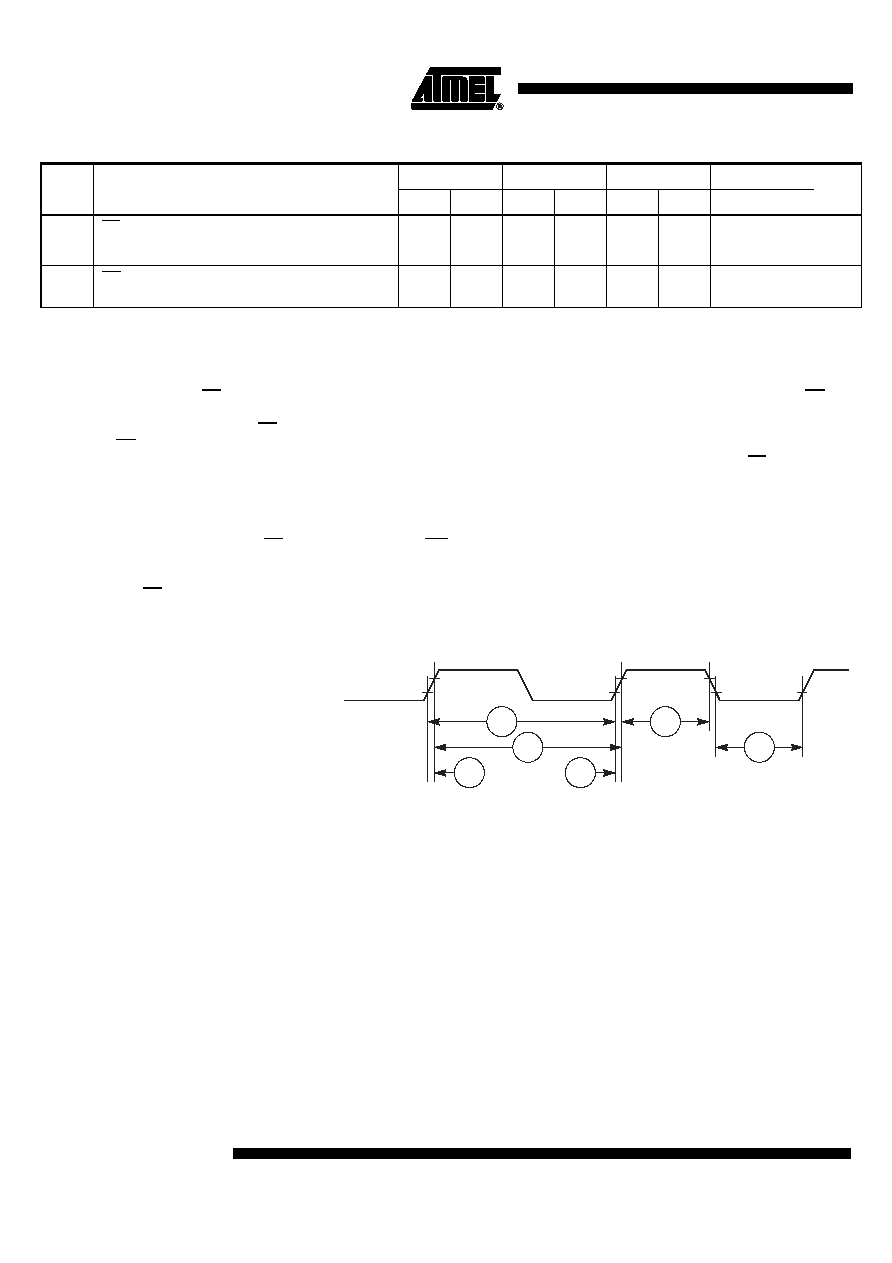

Figure 8. External Clock Timing

B41

TS valid to CLKOUT Rising Edge (SetUp Time).

7

–

7

–

7

–

7

–

ns

B42

CLKOUT Rising Edge to TS Valid (Hold Time).

2

–

2

–

2

–

2

–

ns

B43

AS negation to Memory Controller Signals

Negation

–TBD

–

TBD

–TBD

ns

Table 8. Bus Operation Timings (Continued)

Num

Characteristic

33 MHz

40 MHz

50 MHz

66 MHz

Unit

Min

Max

Min

Max

Min

Max

Min

Max

CLKOUT

B1

B5

B3

B4

B1

B2

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TSPD11CGVRA0 | PUSHBUTTON SWITCH, SPST, MOMENTARY, 0.02A, 20VDC, THROUGH HOLE-RIGHT ANGLE |

| 2-1437573-9 | PUSHBUTTON SWITCH, SPDT, MOMENTARY, 0.02A, 20VDC, SURFACE MOUNT-RIGHT ANGLE |

| 3-1437573-4 | PUSHBUTTON SWITCH, SPST, MOMENTARY, 0.02A, 20VDC, THROUGH HOLE-RIGHT ANGLE |

| TSPF5400AS21 | 5 mm, 1 ELEMENT, INFRARED LED, 870 nm |

| TSS11DGRA | SLIDE SWITCH, SPDT, LATCHED, 0.02A, 20VDC, THROUGH HOLE-RIGHT ANGLE |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TSPC860SRMZQU66D | 制造商:e2v technologies 功能描述:MPU RISC 32BIT 66MHZ 3.3V 357BGA - Trays |

| TSPC860SRVZQU66D | 制造商:e2v technologies 功能描述:TSPC860SRVZQU66D - Trays |

| TSPC860XRMZPU66D | 制造商:ATMEL 制造商全稱(chēng):ATMEL Corporation 功能描述:Integrated Communication Processor |

| TSPC860XRMZQU66D | 制造商:ATMEL 制造商全稱(chēng):ATMEL Corporation 功能描述:Integrated Communication Processor |

| TSPC860XRVZPU66D | 制造商:ATMEL 制造商全稱(chēng):ATMEL Corporation 功能描述:Integrated Communication Processor |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。