- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄368672 > TMS320UVC5402 (Texas Instruments, Inc.) Fixed-Point Digital Signal Processor(定點(diǎn)DSP) PDF資料下載

參數(shù)資料

| 型號(hào): | TMS320UVC5402 |

| 廠商: | Texas Instruments, Inc. |

| 元件分類(lèi): | 數(shù)字信號(hào)處理 |

| 英文描述: | Fixed-Point Digital Signal Processor(定點(diǎn)DSP) |

| 中文描述: | 定點(diǎn)數(shù)字信號(hào)處理器(定點(diǎn)DSP)的 |

| 文件頁(yè)數(shù): | 54/60頁(yè) |

| 文件大小: | 772K |

| 代理商: | TMS320UVC5402 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)當(dāng)前第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)

TMS320UVC5402

FIXED-POINT DIGITAL SIGNAL PROCESSOR

SPRS100A – APRIL 1999 – REVISED AUGUST 1999

54

POST OFFICE BOX 1443

HOUSTON, TEXAS 77251–1443

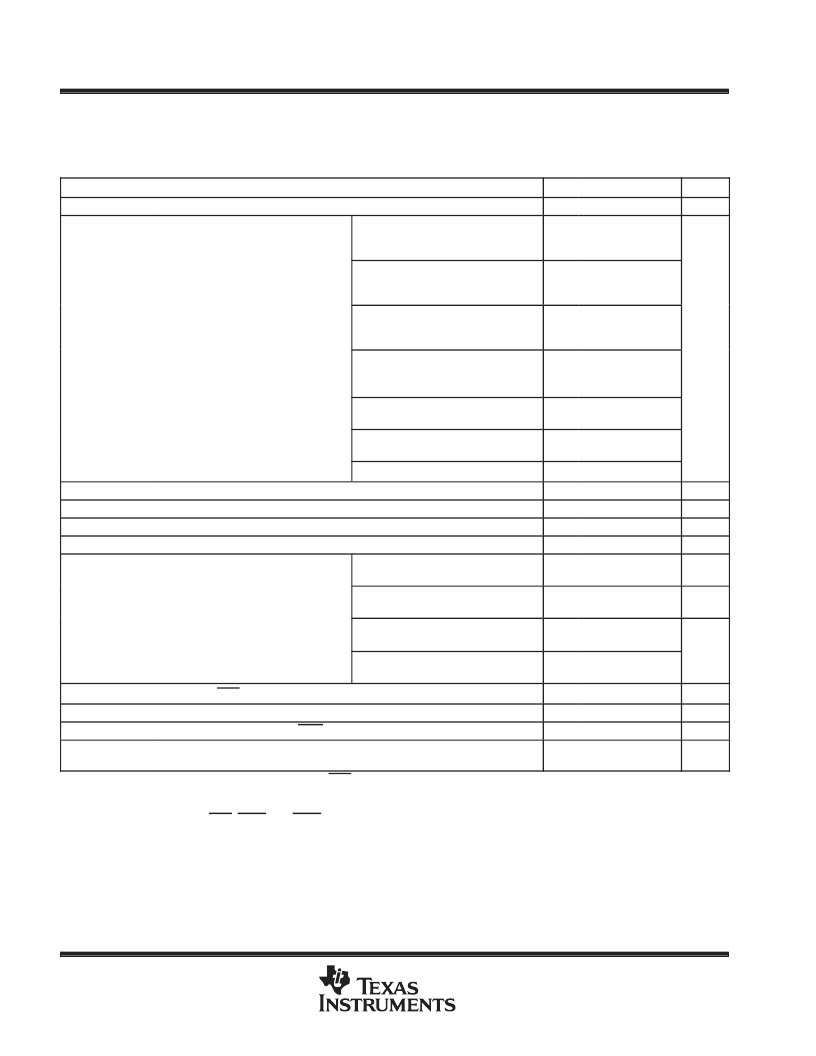

HPI8 timing

switching characteristics over recommended operating conditions§ [H = 0.5t

c(CO)

]

(see Figure 31, Figure 32, Figure 33, and Figure 34)

PARAMETER

MIN

MAX

UNIT

ten(DSL-HD)

Enable time, HD driven from DS low

10

25

ns

Case 1a: Memory accesses when

DMAC is active in 16-bit mode and

tw(DSH) < 18H

Case 1b: Memory accesses when

DMAC is active in 16-bit mode and

tw(DSH)

≥

18H

Case 1c: Memory access when

DMAC is active in 32-bit mode and

tw(DSH) < 26H

Case 1d: Memory access when

DMAC is active in 32-bit mode and

tw(DSH)

≥

26H

18H+20–tw(DSH)

20

td(DSL HDV1)

td(DSL-HDV1)

Delay time, DS low to HDx valid for

first byte of an HPI read

26H+20–tw(DSH)

ns

20

Case 2a: Memory accesses when

DMAC is inactive and tw(DSH) < 10H

Case 2b: Memory accesses when

DMAC is inactive and tw(DSH)

≥

10H

Case 3: Register accesses

10H+20–tw(DSH)

20

20

td(DSL-HDV2)

th(DSH-HDV)R

tv(HYH-HDV)

td(DSH-HYL)

Delay time, DS low to HDx valid for second byte of an HPI read

20

ns

Hold time, HDx valid after DS high, for a HPI read

5

10

ns

Valid time, HDx valid after HRDY high

8

Delay time, DS high to HRDY low (see Note 1)

10

ns

Case 1a: Memory accesses when

DMAC is active in 16-bit mode

18H+15

ns

td(DSH-HYH)

Delay time DS high to HRDY high

Delay time, DS high to HRDY high

Case 1b: Memory accesses when

DMAC is active in 32-bit mode

26H+15

ns

Case 2: Memory accesses when

DMAC is inactive

10H+15

ns

Case 3: Write accesses to HPIC

register (see Note 2)

6H+15

td(HCS-HRDY)

td(COH-HYH)

td(COH-HTX)

Delay time, HCS low/high to HRDY low/high

15

ns

Delay time, CLKOUT high to HRDY high

15

ns

Delay time, CLKOUT high to HINT change

15

ns

td(COH-GPIO)

Delay time, CLKOUT high to HDx output change. HDx is configured as a

general-purpose output.

1. The HRDY output is always high when the HCS input is high, regardless of DS timings.

2. This timing applies when writing a one to the DSPINT bit or HINT bit of the HPIC register. All other writes to the HPIC occur

asynchronoulsy, and do not cause HRDY to be deasserted.

DS refers to the logical OR of HCS, HDS1, and HDS2.

HDx refers to any of the HPI data bus pins (HD0, HD1, HD2, etc.).

§DMAC stands for direct memory access (DMA) controller. The HPI8 shares the internal DMA bus with the DMAC, thus HPI8 access times are

affected by DMAC activity.

GPIO refers to the HD pins when they are configured as general-purpose input/outputs.

8

ns

NOTES:

P

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TMS320VC5409PGE-100 | 16-Bit Digital Signal Processor |

| TMS320VC5409GGU-100 | 16-Bit Digital Signal Processor |

| TMS370C736AFNT | 8-BIT MICROCONTROLLER |

| SE370C758BFZT | 8-BIT MICROCONTROLLER |

| SE370C758BJNT | 8-BIT MICROCONTROLLER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TMS320V34PJ | 制造商:Texas Instruments 功能描述: |

| TMS320V34PJX2 | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Texas Instruments 功能描述: |

| TMS320V640AGDK4 | 制造商:Texas Instruments 功能描述:TMS320DM640 548PIN FCBGA PG2.0 400 MHZ - Trays |

| TMS320V640AGNZ4 | 制造商:Texas Instruments 功能描述:TMS320DM640 548PIN FCBGA PG2.0 - Trays |

| TMS320V641AGDK5 | 制造商:Texas Instruments 功能描述:TMS320DM641AGDK PG2 548 PIN FCBGA 500MHZ - Trays |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。