- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄361947 > TMP320LC2401APZS (Texas Instruments, Inc.) DSP CONTROLLERS PDF資料下載

參數(shù)資料

| 型號(hào): | TMP320LC2401APZS |

| 廠商: | Texas Instruments, Inc. |

| 元件分類: | 數(shù)字信號(hào)處理 |

| 英文描述: | DSP CONTROLLERS |

| 中文描述: | DSP控制器 |

| 文件頁(yè)數(shù): | 6/134頁(yè) |

| 文件大?。?/td> | 1759K |

| 代理商: | TMP320LC2401APZS |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)當(dāng)前第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)

TMS320LF2407A,TMS320LF2406A,TMS320LF2403A,TMS320LF2402A

TMS320LC2406A,TMS320LC2404A,TMS320LC2403A,TMS320LC2402A

DSP CONTROLLERS

SPRS145K

JULY 2000

REVISED AUGUST 2005

6

POST OFFICE BOX 1443

HOUSTON, TEXAS 77251

1443

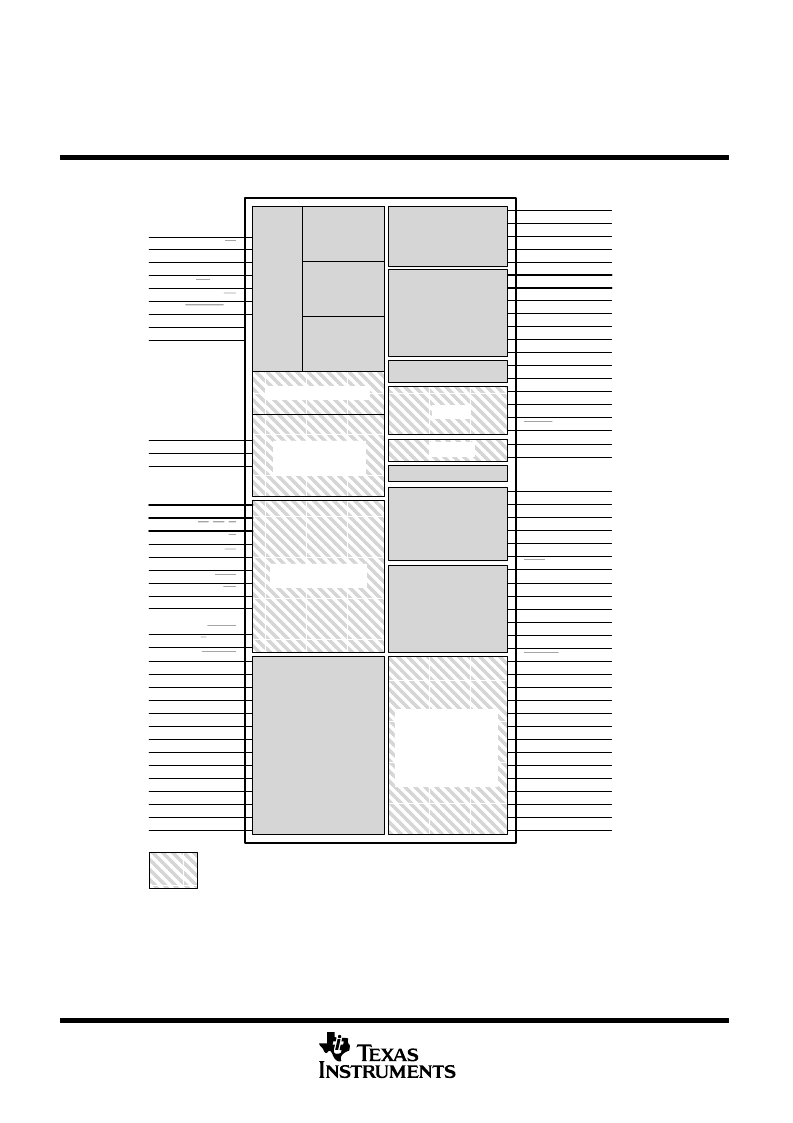

functional block diagram of the 2407A DSP controller

XTAL1/CLKIN

XTAL2

ADCIN00

ADCIN07

PLLV

CCA

PLLF2

PLLF

V

SSA

V

REFHI

V

REFLO

ADCIN08

ADCIN15

V

CCA

SCIRXD/IOPA1

SPISIMO/IOPC2

XINT2/ADCSOC/IOPD0

SCITXD/IOPA0

Port A(0

7) IOPA[0:7]

SPICLK/IOPC4

SPISTE/IOPC5

SPISOMI/IOPC3

Port E(0

7) IOPE[0:7]

Port F(0

6) IOPF[0:6]

TRST

Port C(0

7) IOPC[0:7]

Port D(0) IOPD[0]

Port B(0

7) IOPB[0:7]

TDO

TDI

TMS

CANRX/IOPC7

CANTX/IOPC6

EMU1

PDPINTB

TCK

EMU0

CAP5/QEP4/IOPF0

CAP6/IOPF1

CAP4/QEP3/IOPE7

PWM7/IOPE1

PWM8/IOPE2

PWM10/IOPE4

PWM9/IOPE3

PWM11/IOPE5

PWM12/IOPE6

T4PWM/T4CMP/IOPF3

TDIRB/IOPF4

TCLKINB/IOPF5

T3PWM/T3CMP/IOPF2

DARAM (B0)

256 Words

DARAM (B1)

256 Words

DARAM (B2)

32 Words

C2xx

DSP

Core

PLL Clock

10-Bit ADC

(With Twin

Autosequencer)

èèèèèèè

èèèèèèè

èèèèèèè

èèèèèèè

èèèèèèè

èèèèèèè

èèèèèèèèèèèèè

èèèèèèè

èèèèèèè

èèèèèèè

èèèèèèè

èèèèèèè

èèèèèèè

èèèèèèè

èèèèèèè

èèèèèèè

RS

CLKOUT/IOPE0

XINT1/IOPA2

BIO/IOPC1

MP/MC

TMS2

A0

A15

D0

D15

TP1

TP2

BOOT_EN/XF

V

DD

(3.3 V)

READY

STRB

R/W

RD

PS, DS, IS

VIS_OE

ENA_144

WE

CAP3/IOPA5

PWM1/IOPA6

PWM2/IOPA7

CAP1/QEP1/IOPA3

CAP2/QEP2/IOPA4

PDPINTA

PWM5/IOPB2

PWM6/IOPB3

PWM3/IOPB0

PWM4/IOPB1

T2PWM/T2CMP/IOPB5

T1PWM/T1CMP/IOPB4

TCLKINA/IOPB7

TDIRA/IOPB6

V

SS

V

CCP

(5V)

èèèèèèè

èèèèèèèèèèèèè

èèèèèèèèèèèèè

èèèèèèèèèèèèè

èèèèèèèèèèèèè

èèèèèèèèèèèèè

èèèèèèè

èèèèèèè

Flash/ROM

4K/12K/12K/4K)

External Memory

Event Manager A

3

×

Capture Input

6

×

Compare/PWM

Output

2

×

GP

Timers/PWM

SCI

Digital I/O

(Shared With

Other Pins)

CAN

JTAG Port

Event Manager B

3

×

Capture Input

Output

2

GP

Timers/PWM

èèè

èèè

èèè

Indicates optional modules

.

The memory size and peripheral selection of these modules change for different 240xA devices.

See Table 1 for device-specific details.

W/R / IOPC0

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 5082-7661-CG400 | 7.6 mm (0.3 inch)/10.9 mm (0.43 inch) Seven Segment Displays |

| 74ACT823LMQB | 9-Bit D Flip-Flop |

| 50E-2C-38.0 | TRANS PREBIASED PNP 200MW SOT23 |

| 500E-3CL-5.5 | E Rated Medium Voltage Fuses |

| 500E-3C-5.5 | E Rated Medium Voltage Fuses |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TMP320LC2401AVFA | 制造商:TI 制造商全稱:Texas Instruments 功能描述:DSP CONTROLLERS |

| TMP320LC2401AVFS | 制造商:TI 制造商全稱:Texas Instruments 功能描述:DSP CONTROLLERS |

| TMP320LC2402APAGA | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:DSP|16-BIT|CMOS|TQFP|64PIN|PLASTIC |

| TMP320LC2402APAGS | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:DSP|16-BIT|CMOS|TQFP|64PIN|PLASTIC |

| TMP320LC2402APGA | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:DSP|16-BIT|CMOS|QFP|64PIN|PLASTIC |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。