- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄361947 > TMP320LC2401APZS (Texas Instruments, Inc.) DSP CONTROLLERS PDF資料下載

參數(shù)資料

| 型號: | TMP320LC2401APZS |

| 廠商: | Texas Instruments, Inc. |

| 元件分類: | 數(shù)字信號處理 |

| 英文描述: | DSP CONTROLLERS |

| 中文描述: | DSP控制器 |

| 文件頁數(shù): | 16/134頁 |

| 文件大小: | 1759K |

| 代理商: | TMP320LC2401APZS |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁當前第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁

TMS320LF2407A,TMS320LF2406A,TMS320LF2403A,TMS320LF2402A

TMS320LC2406A,TMS320LC2404A,TMS320LC2403A,TMS320LC2402A

DSP CONTROLLERS

SPRS145K

JULY 2000

REVISED AUGUST 2005

16

POST OFFICE BOX 1443

HOUSTON, TEXAS 77251

1443

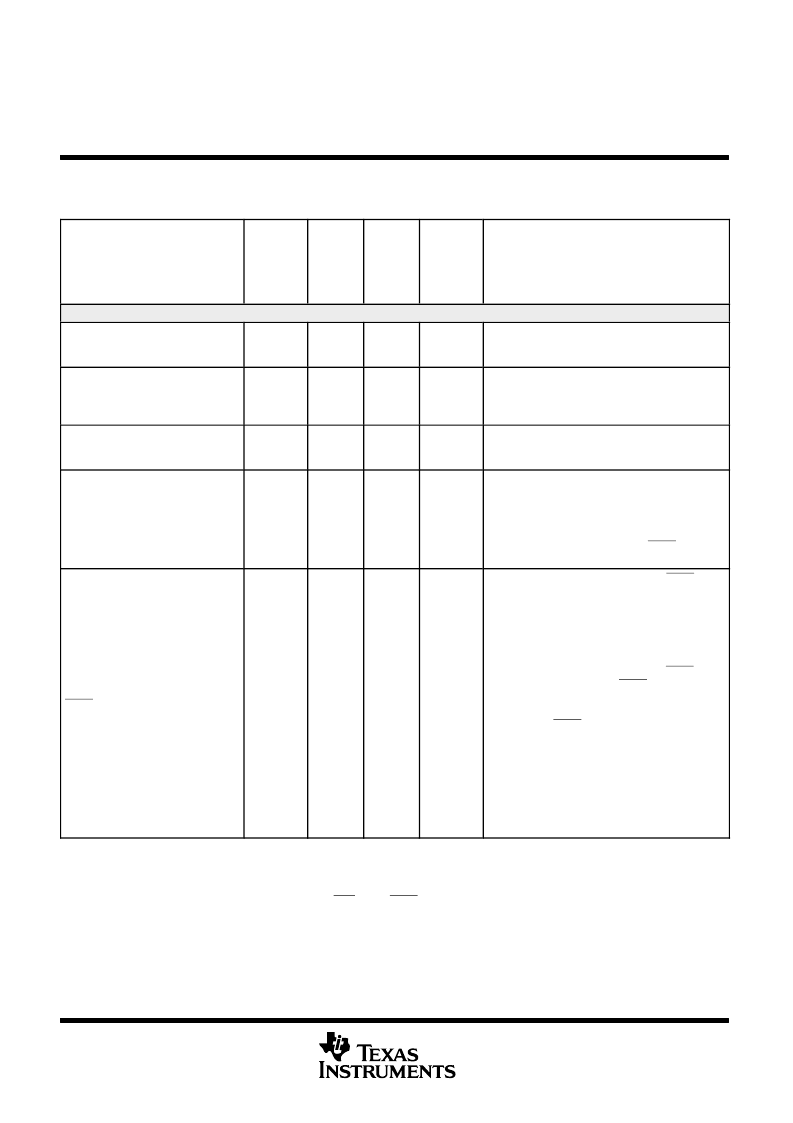

pin functions (continued)

Table 2. LF240xA and LC240xA Pin List and Package Options

(Continued)

PIN NAME

LF2407A

(144-PGE)

2406A

(100-PZ)

LC2404A

(100-PZ)

2403A,

LC2402A

(64-PAG)

and

2402A

(64-PG)

DESCRIPTION

EMULATION AND TEST (CONTINUED)

TDI

139

96

96

30

JTAG test data input (TDI) with internal pullup. TDI

is clocked into the selected register (instruction or

data) on a rising edge of TCK.

(

↑

)

TDO

142

99

99

31

JTAG scan out, test data output (TDO). The

contents of the selected register (instruction or

data) is shifted out of TDO on the falling edge of

TCK.

(

↓

)

JTAG test-mode select (TMS) with internal pullup.

This serial control input is clocked into the TAP

controller on the rising edge of TCK.

TMS

144

100

100

32

(

↑

)

TMS2

36

25

25

48

JTAG test-mode select 2 (TMS2) with internal

pullup. This serial control input is clocked into the

TAP controller on the rising edge of TCK. Used for

test and emulation only. This pin can be left

unconnected in user applications. If the PLL bypass

mode is desired, TMS2, TMS, and TRST should be

held low during reset.

(

↑

)

TRST

1

1

1

33

JTAG test reset with internal pulldown. TRST, when

driven high, gives the scan system control of the

operations of the device. If this signal is not

connected or driven low, the device operates in its

functional mode, and the test reset signals are

ignored.

(

↓

)

NOTE: Do not use pullup resistors on TRST; it has

an internal pulldown device. TRST is an active high

test pin and must be maintained low at all times

during normal device operation. In a low-noise

environment, TRST may be left floating. In other

instances, an external pulldown resistor is highly

recommended. The value of this resistor should be

based on drive strength of the debugger pods

applicable to the design. A 2.2-k

resistor generally

offers

adequate

protection.

application

specific, it is recommended that each

target board be validated for proper operation of the

debugger and the application. (I

↓

)

Since

this

is

Bold, italicized pin names

indicate pin function after reset.

GPIO

General-purpose input/output pin. All GPIOs come up as input after reset.

§

It is highly recommended that V

CCA

be isolated from the digital supply voltage (and V

SSA

from digital ground) to maintain the specified accuracy

and improve the noise immunity of the ADC.

Only when all of the following conditions are met: EMU1/OFF is low, TRST is low, and EMU0 is high

#

No power supply pin (V

DD

, V

DDO

, V

SS

, or V

SSO

) should be left unconnected. All power supply pins must be connected appropriately for proper

device operation.

LEGEND:

↑

Internal pullup

↓

Internal pulldown

(Typical active pullup/pulldown value is

±

16

μ

A.)

相關PDF資料 |

PDF描述 |

|---|---|

| 5082-7661-CG400 | 7.6 mm (0.3 inch)/10.9 mm (0.43 inch) Seven Segment Displays |

| 74ACT823LMQB | 9-Bit D Flip-Flop |

| 50E-2C-38.0 | TRANS PREBIASED PNP 200MW SOT23 |

| 500E-3CL-5.5 | E Rated Medium Voltage Fuses |

| 500E-3C-5.5 | E Rated Medium Voltage Fuses |

相關代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TMP320LC2401AVFA | 制造商:TI 制造商全稱:Texas Instruments 功能描述:DSP CONTROLLERS |

| TMP320LC2401AVFS | 制造商:TI 制造商全稱:Texas Instruments 功能描述:DSP CONTROLLERS |

| TMP320LC2402APAGA | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:DSP|16-BIT|CMOS|TQFP|64PIN|PLASTIC |

| TMP320LC2402APAGS | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:DSP|16-BIT|CMOS|TQFP|64PIN|PLASTIC |

| TMP320LC2402APGA | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:DSP|16-BIT|CMOS|QFP|64PIN|PLASTIC |

發(fā)布緊急采購,3分鐘左右您將得到回復。