- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄361947 > TMP320LC2401APZS (Texas Instruments, Inc.) DSP CONTROLLERS PDF資料下載

參數(shù)資料

| 型號: | TMP320LC2401APZS |

| 廠商: | Texas Instruments, Inc. |

| 元件分類: | 數(shù)字信號處理 |

| 英文描述: | DSP CONTROLLERS |

| 中文描述: | DSP控制器 |

| 文件頁數(shù): | 107/134頁 |

| 文件大?。?/td> | 1759K |

| 代理商: | TMP320LC2401APZS |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁當(dāng)前第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁

TMS320LF2407A, TMS320LF2406A, TMS320LF2403A, TMS320LF2402A

TMS320LC2406A, TMS320LC2404A, TMS320LC2403A, TMS320LC2402A

DSP CONTROLLERS

SPRS145K

JULY 2000

REVISED AUGUST 2005

107

POST OFFICE BOX 1443

HOUSTON, TEXAS 77251

1443

10-bit analog-to-digital converter (ADC)

The 10-bit ADC has a separate power bus for its analog circuitry. These pins are referred to as V

CCA

and V

SSA

.

The power bus isolation is to enhance ADC performance by preventing digital switching noise of the logic

circuitry that can be present on V

SS

and V

CC

from coupling into the ADC analog stage. All ADC specifications

are given with respect to V

SSA

unless otherwise noted.

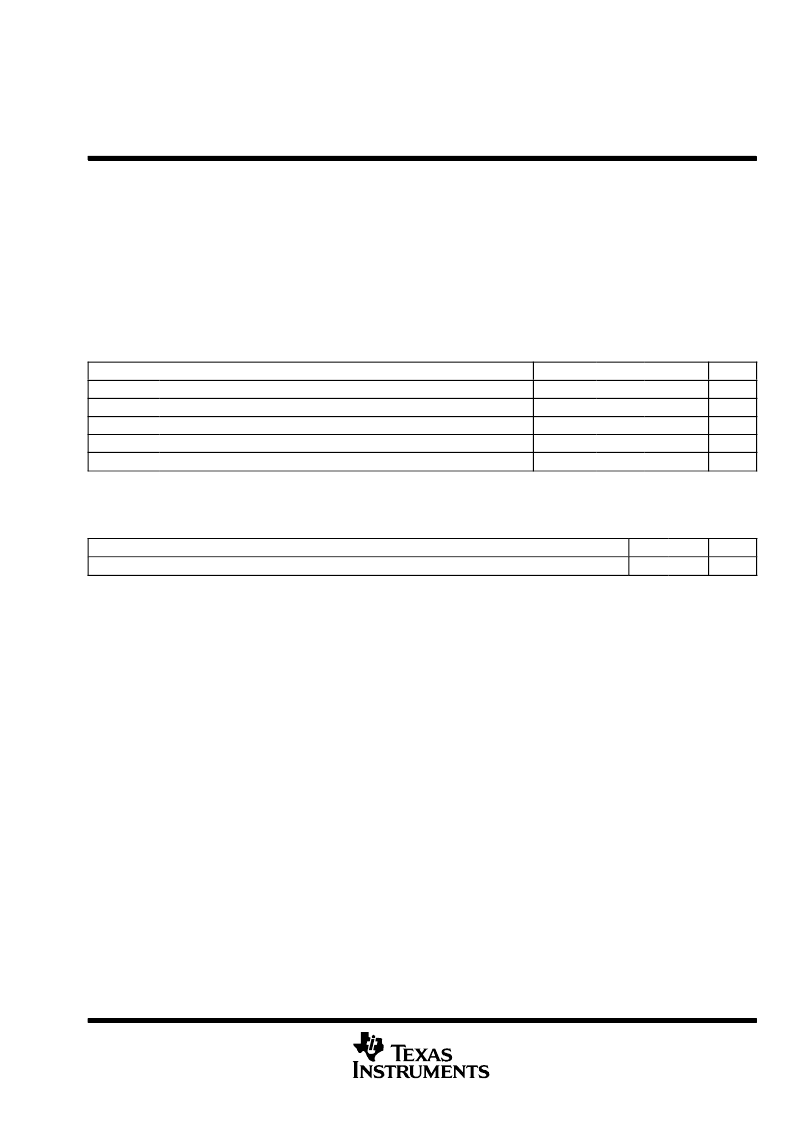

Resolution

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Monotonic

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Output conversion mode

000h to 3FFh (000h for V

I

≤

V

REFLO

; 3FFh for V

I

≥

V

REFHI

)

. . . . . . . . . . . . . . . . . . . .

Minimum conversion time (including sample time)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10-bit (1024 values)

Assured

500 ns

recommended operating conditions

MIN

NOM

MAX

UNIT

V

CCA

V

SSA

V

REFHI

V

REFLO

V

AI

V

REFHI

and V

REFLO

must be stable, within

±

1/2 LSB of the required resolution, during the entire conversion time.

V

REFHI

can be from 2.0 V to V

CCA

; however, the accuracy of the ADC depends on the ground bounce and noise on the target board.

Analog supply voltage

3.0

3.3

3.6

V

Analog ground

Analog supply reference source

Analog ground reference source

0

V

V

CCA

V

V

SSA

V

Analog input voltage, ADCIN00

ADCIN07

V

REFLO

V

REFHI

V

ADC operating frequency

MIN

MAX

UNIT

ADC operating frequency

4

30

MHz

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 5082-7661-CG400 | 7.6 mm (0.3 inch)/10.9 mm (0.43 inch) Seven Segment Displays |

| 74ACT823LMQB | 9-Bit D Flip-Flop |

| 50E-2C-38.0 | TRANS PREBIASED PNP 200MW SOT23 |

| 500E-3CL-5.5 | E Rated Medium Voltage Fuses |

| 500E-3C-5.5 | E Rated Medium Voltage Fuses |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TMP320LC2401AVFA | 制造商:TI 制造商全稱:Texas Instruments 功能描述:DSP CONTROLLERS |

| TMP320LC2401AVFS | 制造商:TI 制造商全稱:Texas Instruments 功能描述:DSP CONTROLLERS |

| TMP320LC2402APAGA | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:DSP|16-BIT|CMOS|TQFP|64PIN|PLASTIC |

| TMP320LC2402APAGS | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:DSP|16-BIT|CMOS|TQFP|64PIN|PLASTIC |

| TMP320LC2402APGA | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:DSP|16-BIT|CMOS|QFP|64PIN|PLASTIC |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。