- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄374697 > SAF82526 (INFINEON TECHNOLOGIES AG) Data Communications ICs PDF資料下載

參數(shù)資料

| 型號: | SAF82526 |

| 廠商: | INFINEON TECHNOLOGIES AG |

| 英文描述: | Data Communications ICs |

| 中文描述: | 數(shù)據(jù)通信集成電路 |

| 文件頁數(shù): | 23/126頁 |

| 文件大小: | 730K |

| 代理商: | SAF82526 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁當(dāng)前第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁

Semiconductor Group

23

82525

82526

82525

82526

SAB

SAB

SAF

SAF

Support of layer-2 functions by HSCX

Beside those bit-oriented functions usually supported with the HDLC protocol, such as bit

stuffing, CRC check, flag and address recognition, the HSCX provides a high degree of

procedural support. In a special operating mode (auto-mode), the HSCX processes the

information transfer and the procedure handshaking (

I

-, and S-frames of HDLC protocol)

autonomously. The only restriction is, that the window size (= number of outstanding

unacknowledged frames) is limited to 1, which will be sufficient in most applications. The

communication procedures are mainly processed between the communication controllers and

not between the processors. Thus the dynamic load of the CPU and the software expense is

largely reduced.

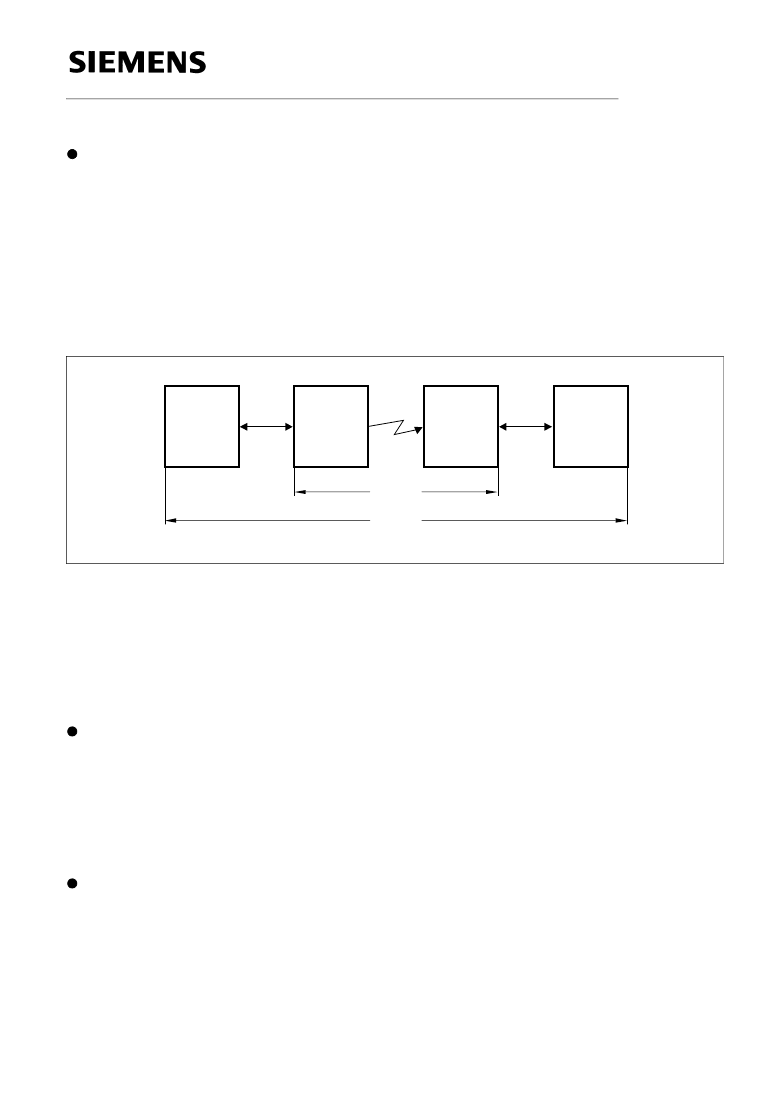

Figure 7

Procedural Support in Auto-Mode

ITS05502

HSCX

HSCX

P

μ

SFrame

Frame

I

Frame

U

μ

P

The CPU is informed about the status of the procedure and has to manage the receive and

transmit data mainly. In order to maintain cost effectiveness and flexibility, such functions as

link setup/disconnection and error recovery in case of protocol errors (U-frames of HDLC

protocols) are not implemented in hardware and must be done by user’s software.

Telecom specific features

In a special operating mode, the HSCX can transmit or receive data packets in one of up to 64

time-slots of programmable width (clock mode 5). Furthermore, the HSCX can transmit or

receive variable data portions within a defined window of one or more clock cycles, which has

to be selected by an external strobe signal (clock mode 1). These features make the HSCX

especially suitable for all applications using time division multiplex methods, such as time-slot

oriented PCM systems, systems designed for packet switching, or in ISDN applications.

FIFO buffers to efficient transfer of data packets.

A further speciality of HSCX are the FIFO buffers used for the temporary storage of data

packets transferred between the serial communications interface and the parallel system bus.

Also because of the overlapping input/output operation (dual-port behaviour), the maximum

message length is not limited by the size of the buffer. Together with the DMA capability, the

dynamic load of the CPU is drastically reduced by transferring the data packets block by block

via direct memory access. The CPU only has to initiate the data transmission by the HSCX and

determine the status in case of completely received frames, but is not involved in data

transfers.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SAF82526N | Data Communications ICs |

| SAB82525 | Data Communications ICs |

| SAB82525H | Data Communications ICs |

| SAF82532H-10 | ICs for Communications |

| SAB82532 | ICs for Communications |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SAF82526HV2.1-HSCX-1 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| SAF82526N | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:Data Communications ICs |

| SAF82526NV2.2 | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC T/E RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| SAF82526NV2.2XT | 制造商:Infineon Technologies AG 功能描述:Communication Controller 44-Pin PLCC T/R |

| SAF82532 | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:ICs for Communications |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。