- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄372114 > SAA7146AH (NXP SEMICONDUCTORS) .012UF/400VDC METAL POLY CAP PDF資料下載

參數(shù)資料

| 型號: | SAA7146AH |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 消費家電 |

| 英文描述: | .012UF/400VDC METAL POLY CAP |

| 中文描述: | SPECIALTY CONSUMER CIRCUIT, PQFP160 |

| 封裝: | 28 X 28 MM, 3.40 MM HEIGHT, PLASTIC, SOT322-2, MS-022, QFP-160 |

| 文件頁數(shù): | 26/144頁 |

| 文件大小: | 645K |

| 代理商: | SAA7146AH |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁當(dāng)前第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁

1998 Apr 09

26

Philips Semiconductors

Product specification

Multimedia bridge, high performance

Scaler and PCI circuit (SPCI)

SAA7146A

7.2.3

A

UDIO

DMA

CONTROL

The SAA7146A provides up to four audio DMA channels,

each using a FIFO of 24 Dwords. Two channels are read

only (A1_in and A2_in) and two channels are write only

(A1_out and A2_out). Because audio represents a

continuous data stream, which is neither line nor field

dependent, the audio DMA control offers only one base

address (BaseAxx) and no pitch register. For FIFO

overflow and underflow the handling of these channels is

done in the same way as the video DMA channels

(see Section 7.2.2).

The protection violation handling differs only if the limit

register and the PV bit are programmed to zero. The audio

DMA channel does not wait for the EOF signal, like the

video ones. It does not generate interrupts. The interrupt

range specified by the limit register is defined in the same

way as described in Section 7.2.2. The audio DMA

channels try immediately to transfer data after setting the

transfer enable bits. All registers for audio DMA control,

which are the base address, the protection address and

the control bits are listed in the following Table 5, except

the input control bits (Burst, Threshold), which are listed in

Table 6.

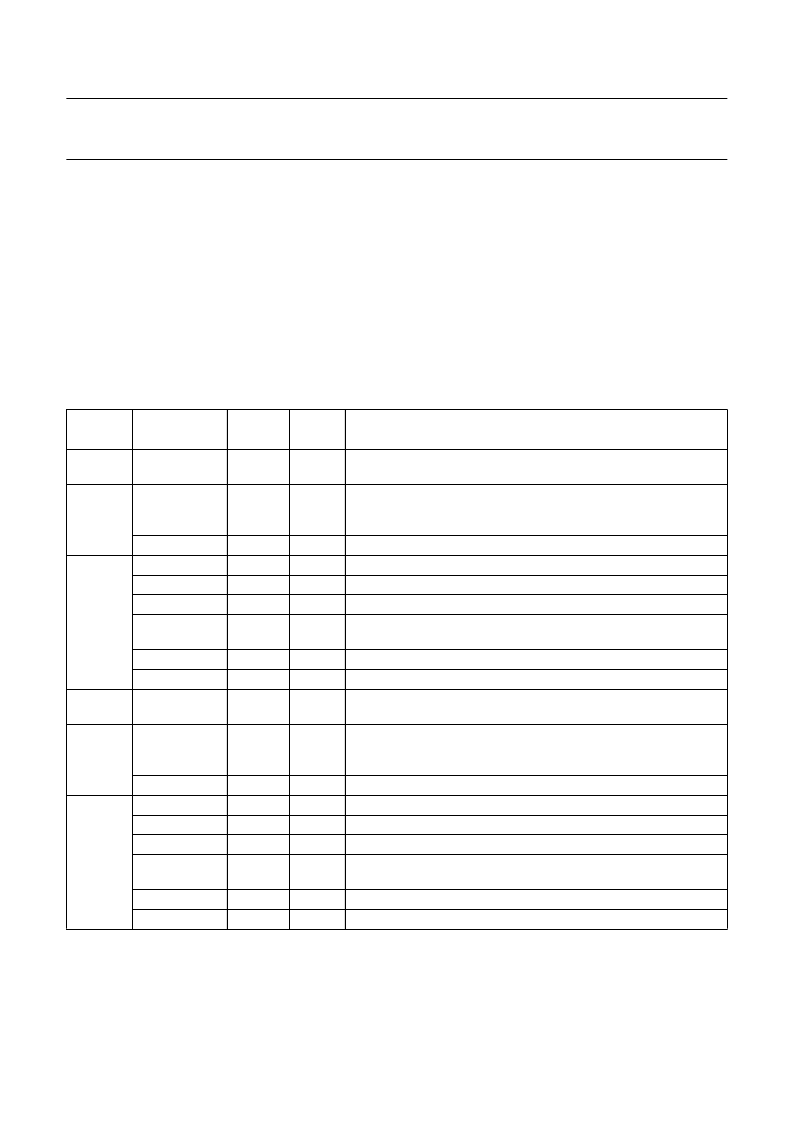

Table 5

Audio DMA control register

OFFSET

(HEX)

NAME

BIT

TYPE

DESCRIPTION

94

BaseA1_in

31 to 0

RW

base address for audio input Channel 1

; this value specifies a

byte address

protection address for audio input Channel 1

; this address

could be used to specify a upper limit for audio access in memory

space

reserved

base address of the page table,

see Section 7.2.4.

mapping enable

; this bit enables the MMU

reserved

interrupt limit

; defines the size of the memory range, that

generates interrupt, if its boundaries are passed

protection violation handling

reserved

Base address for audio output Channel 1

; this value specifies a

byte address. The lower two bits are forced to zero.

protection address for audio output Channel 1

; this address

could be used to specify a upper limit for audio access in memory

space

reserved

base address of the page table

, see Section 7.2.4.

mapping enable

; this bit enables the MMU

reserved

interrupt limit

; defines the size of the memory range, that

generates an interrupt, if its boundaries are passed

protection violation handling

reserved

98

ProtA1_in

31 to 2

RW

PageA1_in

MEA1_in

LimitA1_in

1 to 0

31 to 12

11

10 to 8

7 to 4

9C

RW

RW

RW

PVA1_in

BaseA1_out

3

RW

RW

2 to 0

31 to 0

A0

A4

ProtA1_out

31 to 2

RW

PageA1_out

MEA1_out

LimitA1_out

1 and 0

31 to 12

11

10 to 8

7 to 4

A8

RW

RW

RW

PVA1_out

3

RW

2 to 0

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SAA7146A | Multimedia bridge, high performance Scaler and PCI circuit SPCI |

| SAA7151 | Digital multistandard colour decoder with SCART interface DMSD2-SCART |

| SAA7151B | Digital multistandard colour decoder with SCART interface DMSD2-SCART |

| SAA7157 | Clock signal generator circuit for digital TV systems SCGC |

| SAA7157T | Clock signal generator circuit for digital TV systems SCGC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SAA7146AH/V3,557 | 制造商:NXP Semiconductors 功能描述: |

| SAA7146AH/V4,557 | 功能描述:視頻 IC VIDEO PCI BRIDGE (QFP160) RoHS:否 制造商:Fairchild Semiconductor 工作電源電壓:5 V 電源電流:80 mA 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-28 封裝:Reel |

| SAA7146AH-V4.557 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Multimedia bridge, high performance Scaler and PCI circuit |

| SAA7146AHZ | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Multimedia bridge, high performance Scaler and PCI circuit SPCI |

| SAA7151 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Digital multistandard colour decoder with SCART interface DMSD2-SCART |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。