- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄372109 > SAA3323H (NXP SEMICONDUCTORS) Drive processor for DCC systems PDF資料下載

參數(shù)資料

| 型號(hào): | SAA3323H |

| 廠(chǎng)商: | NXP SEMICONDUCTORS |

| 元件分類(lèi): | 消費(fèi)家電 |

| 英文描述: | Drive processor for DCC systems |

| 中文描述: | SPECIALTY CONSUMER CIRCUIT, PQFP80 |

| 封裝: | 12 X 12 MM, 1.40 MM HEIGHT, PLASTIC, SOT-315-1, TQFP-80 |

| 文件頁(yè)數(shù): | 12/56頁(yè) |

| 文件大小: | 274K |

| 代理商: | SAA3323H |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)當(dāng)前第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)

May 1994

12

Philips Semiconductors

Preliminary specification

Drive processor for DCC systems

SAA3323

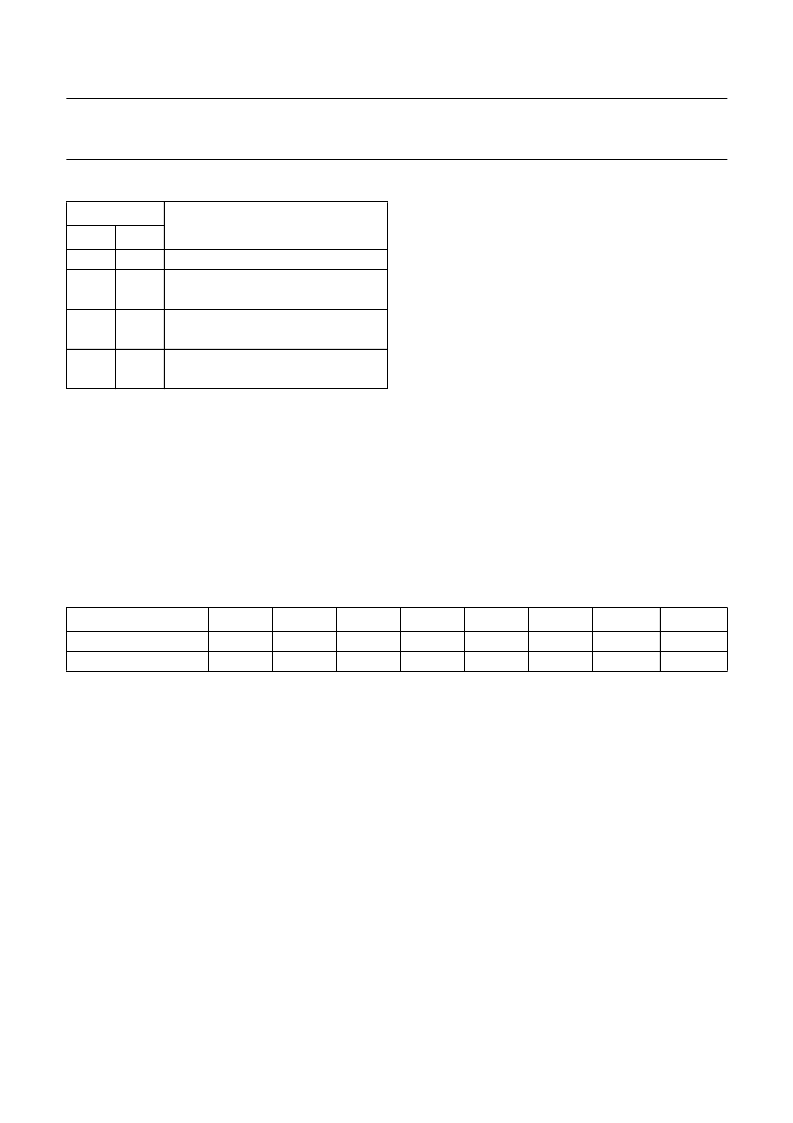

Table 11

SH1 and SH2 (FIR output scaling).

Transfer of FIR coefficients

For the main data channels (tracks 0 to 7) there are

10 coefficients (taps) each of 8 bits, where all of the data

channels make use of the same coefficients. The

addresses for the main data coefficients 0 to 9 are

0 to 9

dec

respectively.

There are ten coefficients (taps) each of 8 bits for the aux

channel (CHAUX). The addresses for the auxiliary

coefficients 0 to 9 are 16 to 25

dec

respectively.

SH

EFFECT ON FIR OUTPUT

1

0

0

0

0

1

FIR mod 256

mod 256

1

0

mod 256

1

1

mod 256

2

FIR

F4

8

FIR

There are 2 banks of coefficients for both the aux and the

main data channels, namely the ‘buffer’, and the ‘a(chǎn)ctive’

banks. The microcontroller writes only to the ‘buffer’

banks, and reads only from the ‘a(chǎn)ctive’ banks.

The microcontroller can poll the digital equalizer status bit

BKSW to see when the switch occurs. BKSW starts life

LOW, goes HIGH as a result of the bank switching and

goes LOW as result of the complete value of a main data

coefficient being received by the digital equalizer.

The microcontroller sets

μ

CS HIGH before sending the

new set of aux or main data coefficients, the digital

equalizer resets it once the bank switch occurs.

The actual FIR coefficients that are used are a function of

the tape head, read amplifier and type of tape (i.e.

pre-recorded or own recorded) used, such information is

outside of the scope of this data sheet.

Coefficient address counter (COEFCNT)

This 5 bit counter is used to point to the FIR coefficient to

be transferred to or from the digital equalizer.

Table 12

Coefficient address counter.

BIT

7

0

6

0

5

0

4

3

2

1

0

Meaning

Default

CC4

0

CC3

0

CC2

0

CC1

0

CC0

0

Pin explanations and interfacing to other hardware

RESET

This is an active HIGH input which resets the SAA3323

and brings it into its default mode, DPAP. This reset does

not affect the contents of the FIR filter coefficients in the

digital equalizer. This should be connected to the system

reset, which can be driven by the microcontroller. The

duration of the reset pulse should be at least 15

μ

s.

SLEEP

This pin is an active HIGH input which puts the SAA3323

in a low power consumption SLEEP mode. This pin should

be connected to the DCC SLEEP signal, which can be

driven by the microcontroller. The CLK24 clock may be

stopped and the VREFP and VREFN inputs brought to

ground while the SAA3323 is in ‘sleep’ mode to further

reduce power consumption. When recovering from sleep

mode, the SLEEP pin should be taken LOW and the

SAA3323 reset.

CLK24

This is the 24.576 MHz clock input and should be

connected directly to the SAA2003 (pin CLK24).

Sub-band serial PASC interface connections

The timing for the sub-band serial PASC interface is given

in Figs 5 to 7.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SAA3500H | Digital audio broadcast channel decoder |

| SAA4700T | VPS dataline processor |

| SAA4700 | VPS dataline processor |

| SAA4945H | LIne MEmory noise Reduction IC LIMERIC |

| SAA4951 | RES 6.49K OHM 1/16W 0.5% 0402SMD |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SAA33299003 | 制造商:LG Corporation 功能描述:S/W,Firmware |

| SAA33308202 | 制造商:LG Corporation 功能描述:S/W,Firmware |

| SAA33333703 | 制造商:LG Corporation 功能描述:S/W,Firmware |

| SAA33378323 | 制造商:LG Corporation 功能描述:S/W,Firmware |

| SAA33378405 | 制造商:LG Corporation 功能描述:S/W,Firmware |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。