- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373330 > RTL8139D(L) RTL8139D(L) Specification PDF資料下載

參數(shù)資料

| 型號: | RTL8139D(L) |

| 英文描述: | RTL8139D(L) Specification |

| 中文描述: | RTL8139D(長)規(guī)格 |

| 文件頁數(shù): | 20/58頁 |

| 文件大?。?/td> | 616K |

| 代理商: | RTL8139D(L) |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁當前第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁

RTL8100B(L)

2001-11-9

Rev.1.41

20

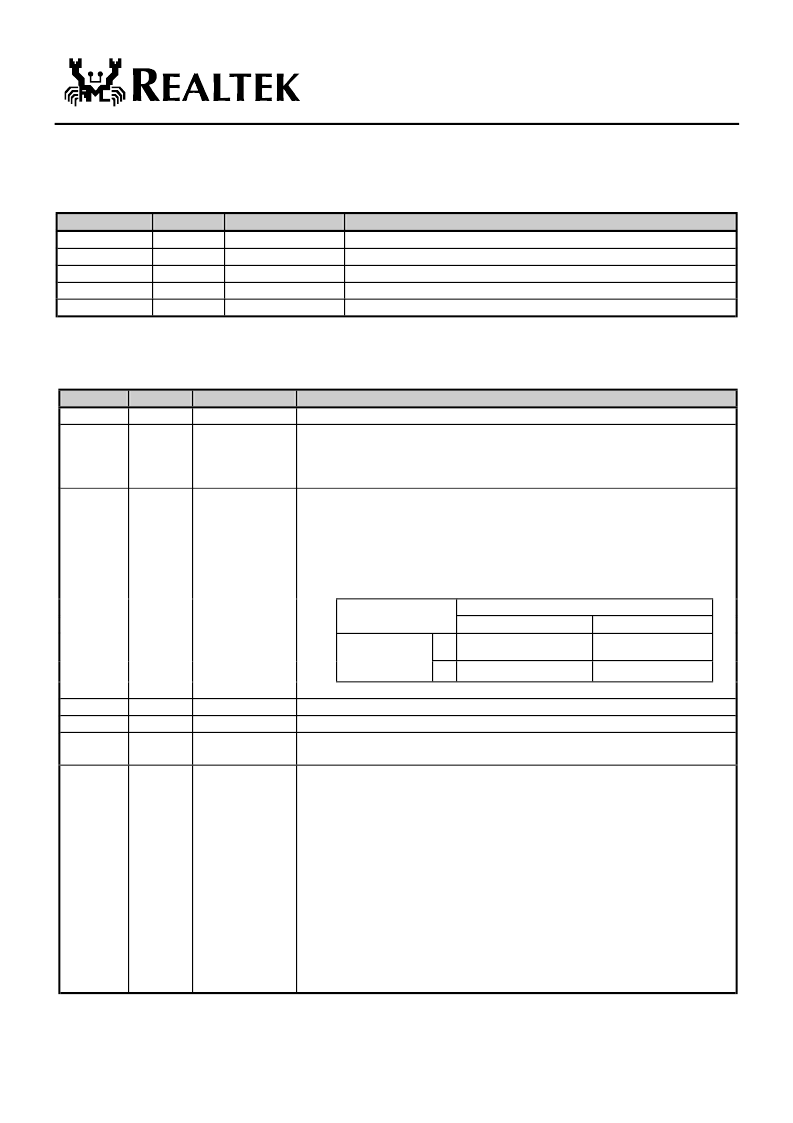

5.10 CONFIG 0: Configuration Register 0

(Offset 0051h, R/W)

Bit

7

6

5

4-3

2-0

R/W

R

R

R

R

-

Symbol

SCR

PCS

T10

PL1, PL0

-

Description

Scrambler Mode:

Always 0.

PCS Mode:

Always 0.

10 Mbps Mode:

Always 0.

Select 10 Mbps medium type:

Always (PL1, PL0) = (1, 0)

Reserved

5.11 CONFIG 1: Configuration Register 1

(Offset 0052h, R/W)

Bit

7-6

5

R/W

R/W

R/W

Symbol

LEDS1-0

DVRLOAD

Description

Refer to the LED PIN definition. The initial value of these bits comes from the 93C46.

Driver Load:

Software may use this bit to make sure that the driver has been

loaded. Writing 1 is 1. Writing 0 is 0. When the command register bits IOEN,

MEMEN, and BMEN of the PCI configuration space are written, the

RTL8100B(L) will clear this bit automatically.

LWAKE active mode:

The LWACT bit and LWPTN bit in CONFIG4 register

are used to program the LWAKE pin’s output signal. According to the

combination of these two bits, there may be 4 choices of LWAKE signal, i.e.,

active high, active low, positive (high) pulse, and negative (low) pulse. The

output pulse width is about 150 ms.

The default value of each of these two bits is 0, i.e., the default output signal of

LWAKE pin is an active high signal.

0

Active high*

LWPTN

1

Positive pulse

* Default value.

Memory Mapping:

The operational registers are mapped into PCI memory space.

I/O Mapping:

The operational registers are mapped into PCI I/O space.

Set to enable Vital Product Data:

The VPD data is stored in 93C46 from within

offset 40h-7Fh.

Power Management Enable:

Writable only when 93C46CR register EEM1=EEM0=1

Let A denote the New_Cap bit (bit 4 of the Status Register) in the PCI

Configuration space offset 06H.

Let B denote the Cap_Ptr register in the PCI Configuration space offset 34H.

Let C denote the Cap_ID (power management) register in the PCI Configuration

space offset 50H.

Let D denote the power management registers in the PCI Configuration space

offset from 52H to 57H.

Let E denote the Next_Ptr (power management) register in the PCI

Configuration space offset 51H.

LWACT

LWAKE output

0

1

Active low

Negative pulse

4

R/W

LWACT

3

2

1

R

R

MEMMAP

IOMAP

VPD

R/W

0

R/W

PMEn

PMEn Description

1 A=1, B=50h, C=01h, D valid, E=0

0 A=B=C=E=0, D not valid

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| RTL8150 | RTL8150L(M) Specifications |

| RTL8169 | RTL8169 Specification |

| RTL8201L | Layout guide |

| RTL8204 | Layout reference |

| RTL8305SB | RTL8305SB |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| RTL8139D-LF | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:SINGLE-CHIP MULTI-FUNCTION 10/100Mbps ETHERNET CONTROLLER WITH POWER MANAGEMENT |

| RTL8139DL-GR | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:SINGLE-CHIP MULTI-FUNCTION 10/100Mbps ETHERNET CONTROLLER WITH POWER MANAGEMENT |

| RTL8139DL-LF | 制造商:Realtek Semiconductor 功能描述: |

| RTL8139L | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:REALTEK 3.3V SINGLE CHIP FAST ETHERNET CONTROLLER WITH POWER MANAGEMENT |

| RTL8150 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:RTL8150L(M) Specifications |

發(fā)布緊急采購,3分鐘左右您將得到回復。