- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373330 > RTL8139D(L) RTL8139D(L) Specification PDF資料下載

參數(shù)資料

| 型號(hào): | RTL8139D(L) |

| 英文描述: | RTL8139D(L) Specification |

| 中文描述: | RTL8139D(長)規(guī)格 |

| 文件頁數(shù): | 13/58頁 |

| 文件大小: | 616K |

| 代理商: | RTL8139D(L) |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁當(dāng)前第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁

RTL8100B(L)

2001-11-9

Rev.1.41

13

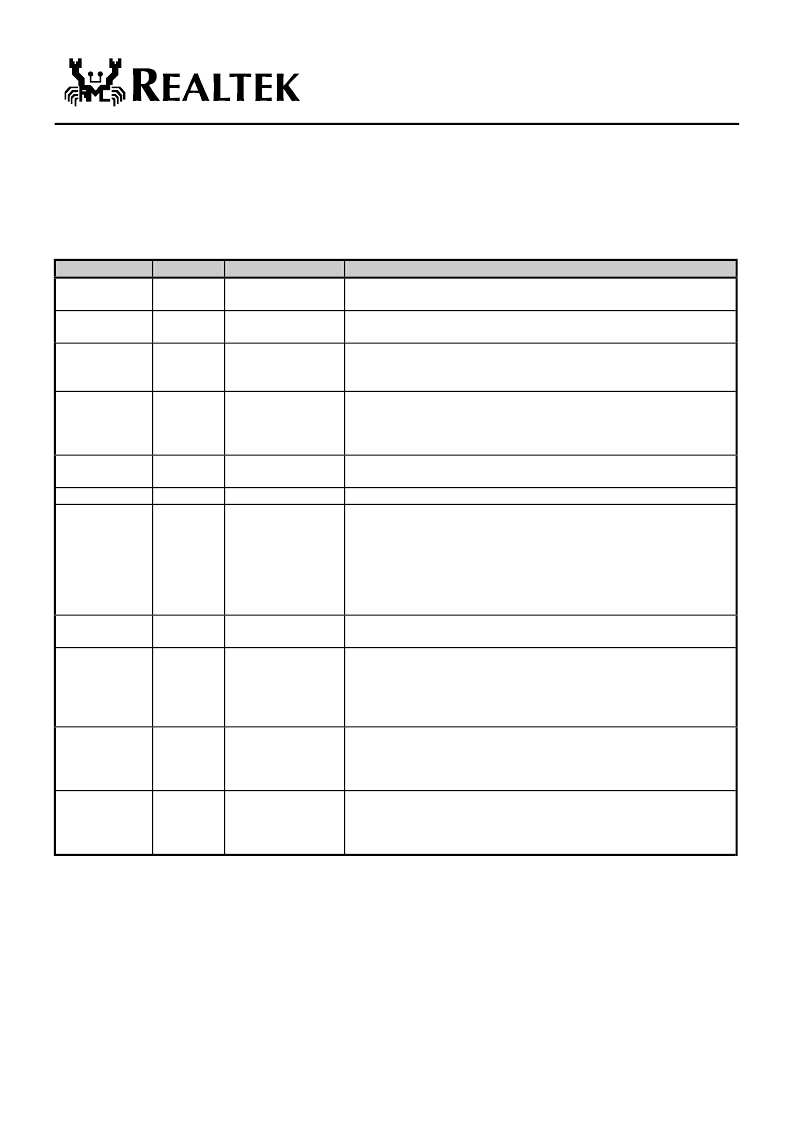

5.2 Transmit Status Register

(TSD0-3)(Offset 0010h-001Fh, R/W)

The read-only bits (CRS, TABT, OWC, CDH, NCC3-0, TOK, TUN) will be cleared by the RTL8100B(L) when the Transmit

Byte Count (bits 12-0) in the corresponding Tx descriptor is written. It is not affected when software writes to these bits. These

registers are only permitted to write by double-word access. After a software reset, all bits except OWN bit are reset to “0”.

Bit

31

R/W

R

Symbol

CRS

Description

Carrier Sense Lost:

This bit is set to 1 when the carrier is lost during

transmission of a packet.

Transmit Abort:

This bit is set to 1 if the transmission of a packet was

aborted. This bit is read only, writing to this bit is not affected.

Out of Window Collision:

This bit is set to 1 if the RTL8100B(L)

encountered an "out of window" collision during the transmission of a

packet.

CD Heart Beat:

The NIC watches for a collision signal (ie, CD

Heartbeat signal) during the first 6.4us of the interframe gap following a

transmission. This bit is set if the transceiver fails to send this signal.

This bit is cleared in the 100 Mbps mode.

Number of Collision Count:

Indicates the number of collisions

encountered during the transmission of a packet.

Reserved

Early Tx Threshold:

Specifies the threshold level in the Tx FIFO to

begin the transmission. When the byte count of the data in the Tx FIFO

reaches this level, (or the FIFO contains at least one complete packet)

the RTL8100B(L) will transmit this packet.

000000 = 8 bytes

These fields count from 000001 to 111111 in unit of 32 bytes.

This threshold must be avoided from exceeding 2K byte.

Transmit OK:

Set to 1 indicates that the transmission of a packet was

completed successfully and no transmit underrun has occurred.

Transmit FIFO Underrun:

Set to 1 if the Tx FIFO was exhausted

during the transmission of a packet. The RTL8100B(L) can re-transfer

data if the Tx FIFO underruns and can also transmit the packet to the

wire successfully even though the Tx FIFO underruns. That is, when

TSD<TUN>=1, TSD<TOK>=0 and ISR<TOK>=1 (or ISR<TER>=1).

OWN:

The RTL8100B(L) sets this bit to 1 when the Tx DMA

operation of this descriptor was completed. The driver must set this bit

to 0 when the Transmit Byte Count (bits 0-12) is written. The default

value is 1.

Descriptor Size:

The total size in bytes of the data in this descriptor. If

the packet length is more than 1792 byte (0700h), the Tx queue will be

invalid, i.e. the next descriptor will be written only after the OWN bit of

that long packet's descriptor has been set.

30

R

TABT

29

R

OWC

28

R

CDH

27-24

R

NCC3-0

23-22

21-16

-

-

R/W

ERTXTH5-0

15

R

TOK

14

R

TUN

13

R/W

OWN

12-0

R/W

SIZE

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| RTL8150 | RTL8150L(M) Specifications |

| RTL8169 | RTL8169 Specification |

| RTL8201L | Layout guide |

| RTL8204 | Layout reference |

| RTL8305SB | RTL8305SB |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| RTL8139D-LF | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:SINGLE-CHIP MULTI-FUNCTION 10/100Mbps ETHERNET CONTROLLER WITH POWER MANAGEMENT |

| RTL8139DL-GR | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:SINGLE-CHIP MULTI-FUNCTION 10/100Mbps ETHERNET CONTROLLER WITH POWER MANAGEMENT |

| RTL8139DL-LF | 制造商:Realtek Semiconductor 功能描述: |

| RTL8139L | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:REALTEK 3.3V SINGLE CHIP FAST ETHERNET CONTROLLER WITH POWER MANAGEMENT |

| RTL8150 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:RTL8150L(M) Specifications |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。