- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373330 > RTL8139D(L) RTL8139D(L) Specification PDF資料下載

參數(shù)資料

| 型號: | RTL8139D(L) |

| 英文描述: | RTL8139D(L) Specification |

| 中文描述: | RTL8139D(長)規(guī)格 |

| 文件頁數(shù): | 18/58頁 |

| 文件大小: | 616K |

| 代理商: | RTL8139D(L) |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁當前第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁

RTL8100B(L)

2001-11-9

Rev.1.41

18

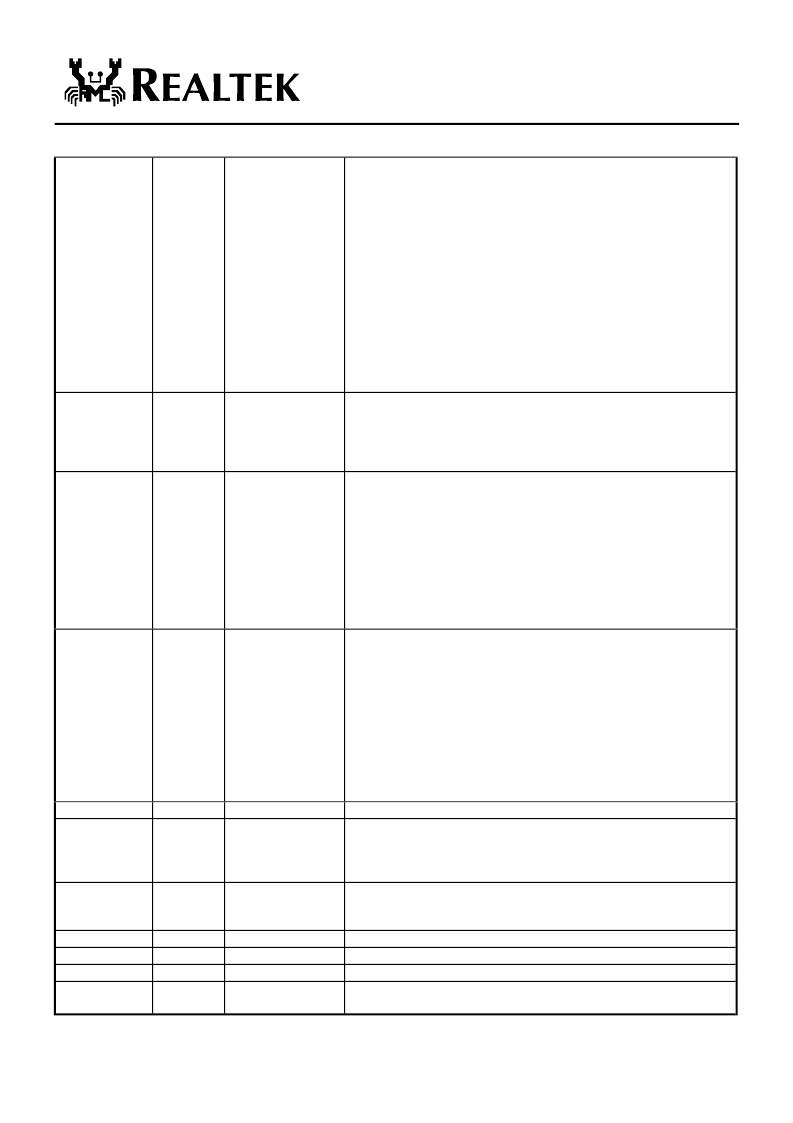

15-13

R/W

RXFTH2, 1, 0

Rx FIFO Threshold:

Specifies Rx FIFO Threshold level. When the

number of the received data bytes from a packet, which is being received

into the RTL8100B(L)'s Rx FIFO, has reached to this level (or the FIFO

has contained a complete packet), the receive PCI bus master function

will begin to transfer the data from the FIFO to the host memory. This

field sets the threshold level according to the following table:

000 = 16 bytes

001 = 32 bytes

010 = 64 bytes

011 = 128 bytes

100 = 256 bytes

101 = 512 bytes

110 = 1024 bytes

111 = No Rx threshold. The RTL8100B(L) begins the transfer of data

after having received a whole packet in the FIFO.

Rx Buffer Length:

This field indicates the size of the Rx ring buffer.

00 = 8k + 16 byte

01 = 16k + 16 byte

10 = 32K + 16 byte

11 = 64K + 16 byte

Max DMA Burst Size per Rx DMA Burst:

This field sets the maximum

size of the receive DMA data bursts according to the following table:

000 = 16 bytes

001 = 32 bytes

010 = 64 bytes

011 = 128 bytes

100 = 256 bytes

101 = 512 bytes

110 = 1024 bytes

111 = Unlimited

When set to 0: The RTL8100B(L) will transfer the rest of the packet data into

the beginning of the Rx buffer if this packet has not been completely moved

into the Rx buffer and the transfer has arrived at the end of the Rx buffer.

When set to 1: The RTL8100B(L) will keep moving the rest of the packet

data into the memory immediately after the end of the Rx buffer, if this

packet has not been completely moved into the Rx buffer and the transfer

has arrived at the end of the Rx buffer. The software driver must reserve at

least 1.5K bytes buffer to accept the remainder of the packet. We assume

that the remainder of the packet is X bytes. The next packet will be moved

into the memory from the X byte offset at the top of the Rx buffer.

This bit is invalid when Rx buffer is selected to 64K bytes.

Reserved

Accept Error Packet:

When set to 1, all packets with CRC error,

alignment error, and/or collided fragments will be accepted. When set to 0,

all packets with CRC error, alignment error, and/or collided fragments will

be rejected.

Accept Runt:

This bit allows the receiver to accept packets that are

smaller than 64 bytes. The packet must be at least 8 bytes long to be

accepted as a runt. Set to 1 to accept runt packets.

Accept Broadcast packets:

Set to 1 to accept, 0 to reject.

Accept Multicast packets:

Set to 1 to accept, 0 to reject.

Accept Physical Match packets:

Set to 1 to accept, 0 to reject.

Accept All Packets:

Set to 1 to accept all packets with a physical

destination address, 0 to reject.

12-11

R/W

RBLEN1, 0

10-8

R/W

MXDMA2, 1, 0

7

R/W

WRAP

6

5

-

-

R/W

AER

4

R/W

AR

3

2

1

0

R/W

R/W

R/W

R/W

AB

AM

APM

AAP

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| RTL8150 | RTL8150L(M) Specifications |

| RTL8169 | RTL8169 Specification |

| RTL8201L | Layout guide |

| RTL8204 | Layout reference |

| RTL8305SB | RTL8305SB |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| RTL8139D-LF | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:SINGLE-CHIP MULTI-FUNCTION 10/100Mbps ETHERNET CONTROLLER WITH POWER MANAGEMENT |

| RTL8139DL-GR | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:SINGLE-CHIP MULTI-FUNCTION 10/100Mbps ETHERNET CONTROLLER WITH POWER MANAGEMENT |

| RTL8139DL-LF | 制造商:Realtek Semiconductor 功能描述: |

| RTL8139L | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:REALTEK 3.3V SINGLE CHIP FAST ETHERNET CONTROLLER WITH POWER MANAGEMENT |

| RTL8150 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:RTL8150L(M) Specifications |

發(fā)布緊急采購,3分鐘左右您將得到回復。