- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370028 > PXA250 (Intel Corp.) Intel-R PXA250 and PXA210 Applications Processors PDF資料下載

參數(shù)資料

| 型號(hào): | PXA250 |

| 廠商: | Intel Corp. |

| 英文描述: | Intel-R PXA250 and PXA210 Applications Processors |

| 中文描述: | 英特爾- R的PXA250和PXA210應(yīng)用處理器 |

| 文件頁數(shù): | 19/46頁 |

| 文件大小: | 431K |

| 代理商: | PXA250 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁當(dāng)前第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁

Electrical, Mechanical, and Thermal Specification

—

PXA250 and PXA210

Datasheet

19

3.1.1.2

PXA210 Signal Pin Descriptions

Signal definitions for the PXA210 applications processor are described in Table 4. The physical

characteristics of the PXA210 applications processor are shown in Figure 3,

“

PXA210

Applications Processor

”

on page 26. The pinout for the PXA210 applications processor is

described in Table 5,

“

PXA210 225-Lead 13x13mm TPBGA Pinout

—

Ballpad Number Order

”

on

page 27.

K14

GPIO[3]

N11

VCCN

T8

nCS[1]/GPIO[15]

K15

PXTAL

N12

DREQ[0]/GPIO[20]

T9

nCS[3]/GPIO[79]

K16

PEXTAL

N13

VCCN

T10

MD[9]

L1

MA[12]

N14

DREQ[1]/GPIO[19]

T11

MD[11]

L2

VSSN

N15

GPIO[21]

T12

MD[14]

L3

MA[13]

N16

nPWAIT/GPIO[56]

T13

nCS[5]/GPIO[33]

L4

MD[20]

P1

MA[17]

T14

nPWE/GPIO[49]

L5

MD[2]

P2

MA[19]

T15

nPIOR/GPIO[50]

L6

VCC

P3

VCCN

T16

VCCN

L7

DQM[3]

P4

MA[25]

L8

MD[28]

P5

MA[23]

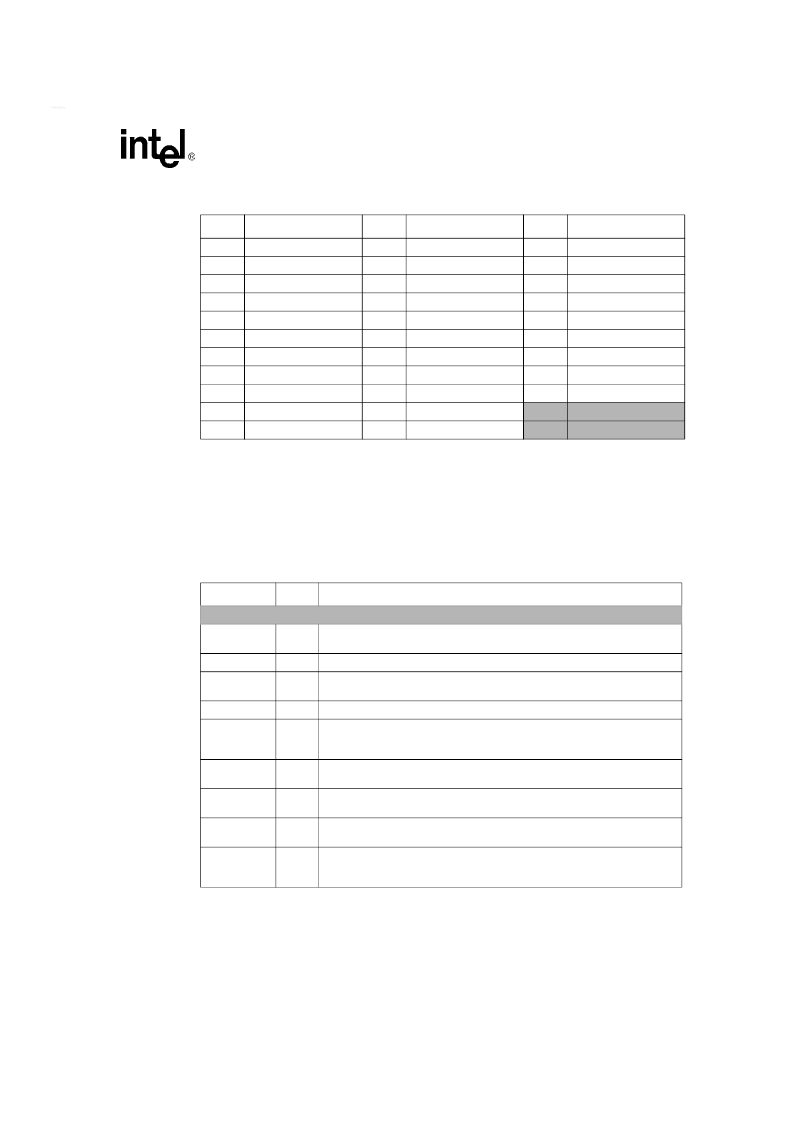

Table 3. PXA250 256-Lead 17x17mm mBGA Pinout

—

Ballpad Number Order (Sheet 3 of 3)

Ball #

Signal

Ball #

Signal

Ball #

Signal

Table 4. Pin and Signal Descriptions for the PXA210 Applications Processor (Sheet 1 of 7)

Pin Name

Type

Signal Descriptions

Memory Controller Pins

MA[25:0]

OCZ

Memory address bus.

(output) Signals the address requested for memory

accesses.

MD[15:0]

ICOCZ

Memory data bus.

(input/output) Lower 16 bits of the data bus.

nOE

OCZ

Memory output enable.

(output) Connect to the output enables of memory

devices to control data bus drivers.

nWE

OCZ

Memory write enable.

(output) Connect to the write enables of memory devices.

nSDCS[1:0]

OCZ

SDRAM CS for banks 1 and 0.

(output) Connect to the chip select (CS) pins for

SDRAM. For the PXA210 applications processor nSDCS0 can be Hi-Z, nSDCS1

cannot.

DQM[1:0]

OCZ

SDRAM DQM for data bytes 1 and 0.

(output) Connect to the data output mask

enables (DQM) for SDRAM.

nSDRAS

OCZ

SDRAM RAS.

(output) Connect to the row address strobe (RAS) pins for all banks

of SDRAM.

nSDCAS

OCZ

SDRAM CAS.

(output) Connect to the column address strobe (CAS) pins for all

banks of SDRAM.

SDCKE[0]

OC

SDRAM and/or Synchronous Static Memory clock enable.

(output) Connect to

the CKE pins of SMROM and SDRAM-timing Synchronous Flash. The memory

controller provides control register bits for deassertion.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PXA255 | PXA255 Processor |

| PXA270 | Electrical, Mechanical, and Thermal Specification |

| PXAC37 | XA 16-bit microcontroller family 32K/1024 OTP CAN transport layer controller 1 UART, 1 SPI Port, CAN 2.0B, 32 CAN ID Filters, transport layer co-proce |

| PXB16050U | NPN microwave power transistor |

| PY08-02 | INDUSTRIERELAIS FASSUNG PCB |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PXA250B2C400 | 制造商:Intel 功能描述:Microprocessor, 32 Bit, 256 Pin, Plastic, BGA |

| PXA250C0C400 | 制造商:Intel 功能描述:IC,MICROPROCESSOR,32-BIT,CMOS,BGA,256PIN,PLASTIC |

| PXA255 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:PXA255 Processor |

| PXA25VC22RMH70TP | 制造商:United Chemi-Con Inc 功能描述:Cap Aluminum 22uF 25V 20% (8 X 6.7mm) SMD 0.05 Ohm 1800mA 2000 hr 105°C T/R |

| PXA270 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Electrical, Mechanical, and Thermal Specification |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。