- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄368020 > PI7C8150 PCI Bridge | 2-Port PCI-to-PCI Bridge PDF資料下載

參數(shù)資料

| 型號: | PI7C8150 |

| 英文描述: | PCI Bridge | 2-Port PCI-to-PCI Bridge |

| 中文描述: | PCI橋| 2端口PCI至PCI橋 |

| 文件頁數(shù): | 94/115頁 |

| 文件大小: | 879K |

| 代理商: | PI7C8150 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁當(dāng)前第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁

PI7C8150B

2-PORT PCI-TO-PCI BRIDGE

ADVANCE INFORMATION

Page 94 of 115

July 31, 2003 – Revision 1.031

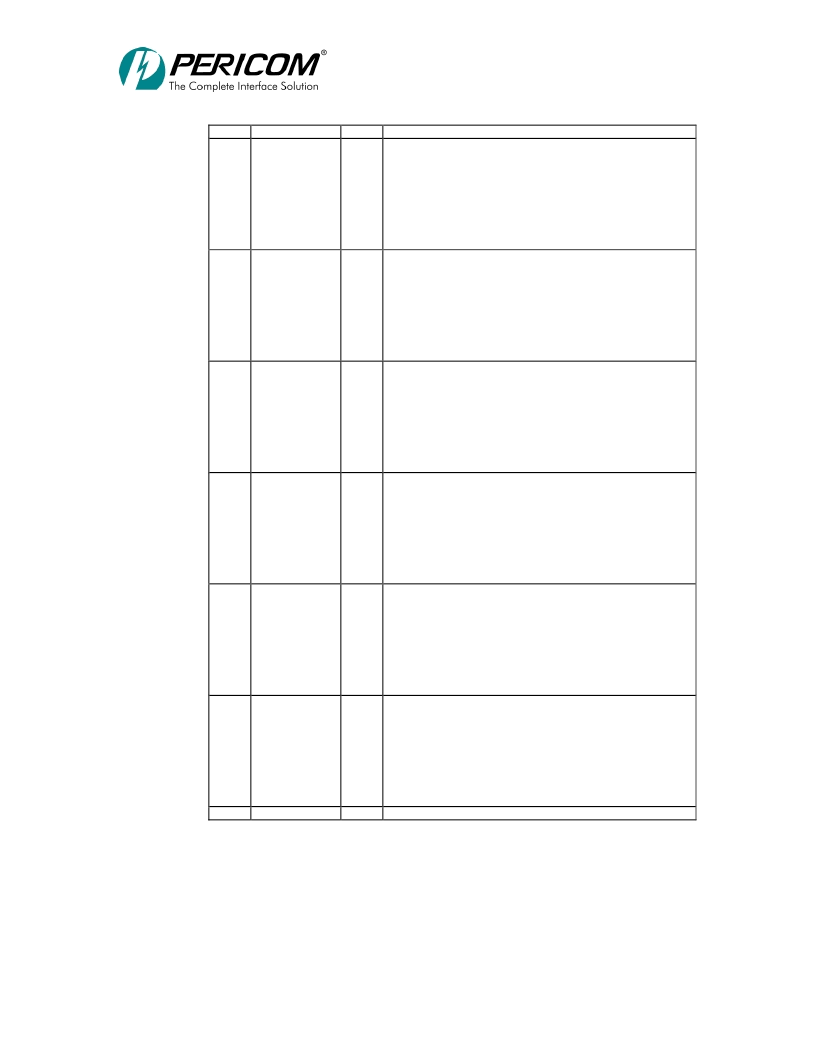

Bit

Function

Type

Description

Controls PI7C8150B’s ability to assert P_SERR_L when it is unable

to transfer any read data from the target after 2

attempts.

0: P_SERR_L is asserted if this event occurs and the SERR_L enable

bit in the command register is set.

1: P_SERR_L is not assert if this event occurs.

Reset to 0

Controls PI7C8150B’s ability to assert P_SERR_L when it is unable

to transfer delayed write data after 2

attempts.

0: P_SERR_L is asserted if this event occurs and the SERR_L enable

bit in the command register is set

1: P_SERR_L is not asserted if this event occurs

Reset to 0

Controls PI7C8150B’s ability to assert P_SERR_L when it receives a

target abort when attempting to deliver posted write data.

0: P_SERR_L is asserted if this event occurs and the SERR_L enable

bit in the command register is set

1: P_SERR_L is not asserted if this event occurs

Reset to 0

Controls PI7C8150B’s ability to assert P_SERR_L when it receives a

master abort when attempting to deliver posted write data.

0: P_SERR# is asserted if this event occurs and the SERR# enable bit

in the command register is set

1: P_SERR# is not asserted if this event occurs

Reset to 0

Controls PI7C8150B’s ability to assert P_SERR# when it is unable to

transfer delayed write data after 2

attempts.

0: P_SERR_L is asserted if this event occurs and the SERR_L enable

bit in the command register is set

1: P_SERR_L is not asserted if this event occurs

Reset to 0

Controls PI7C8150B’s ability to assert P_SERR_L when it is unable

to transfer any read data from the target after 2

attempts.

0: P_SERR_L is asserted if this event occurs and the SERR_L enable

bit in the command register is set

1: P_SERR_L is not asserted if this event occurs

Reset to 0

Reserved. Returns 0 when read. Reset to 0

1

Posted Write

Parity Error

R/W

2

Posted Write

Non-Delivery

R/W

3

Target Abort

During Posted

Write

R/W

4

Master Abort On

Posted Write

R/W

5

Delayed Write

Non-Delivery

R/W

6

Delayed Read –

No Data From

Target

R/W

7

Reserved

R/O

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PI7C8150-33 | PCI Bridge | 2-Port PCI-to-PCI Bridge |

| PI7C8150A | PCI Bridge | 2-Port PCI-to-PCI Bridge |

| PI7C8150A-33 | PCI Bridge | 2-Port PCI-to-PCI Bridge |

| PI7C8150B | PCI Bridge | Asynchronous 2-Port PCI Bridge |

| PI7C8152A | ENHANCED 2- PORT TO PCI BRIDGE INTEL 21152 COMPORISON |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PI7C8150-33 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:PCI Bridge | 2-Port PCI-to-PCI Bridge |

| PI7C8150A | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:PCI Bridge | 2-Port PCI-to-PCI Bridge |

| PI7C8150A-33 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:PCI Bridge | 2-Port PCI-to-PCI Bridge |

| PI7C8150AMA | 制造商:Pericom Semiconductor Corporation 功能描述:PCI to PCI Bridge 208-Pin FQFP |

| PI7C8150AMA-33 | 制造商:Pericom Semiconductor Corporation 功能描述:PCI-to-PCI Bridge 208-Pin FQFP |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。