- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄378045 > PCI4510PDV (Texas Instruments, Inc.) PC CARD AND INTEGRATED 1394A-2000 OHCI TWO PORT PHY/LINK LAYER CONTROLLER PDF資料下載

參數(shù)資料

| 型號: | PCI4510PDV |

| 廠商: | Texas Instruments, Inc. |

| 英文描述: | PC CARD AND INTEGRATED 1394A-2000 OHCI TWO PORT PHY/LINK LAYER CONTROLLER |

| 中文描述: | PC卡和綜合1394A端口- 2000 OHCI的兩個端口物理層/鏈路層控制器 |

| 文件頁數(shù): | 203/220頁 |

| 文件大?。?/td> | 1356K |

| 代理商: | PCI4510PDV |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁第162頁第163頁第164頁第165頁第166頁第167頁第168頁第169頁第170頁第171頁第172頁第173頁第174頁第175頁第176頁第177頁第178頁第179頁第180頁第181頁第182頁第183頁第184頁第185頁第186頁第187頁第188頁第189頁第190頁第191頁第192頁第193頁第194頁第195頁第196頁第197頁第198頁第199頁第200頁第201頁第202頁當前第203頁第204頁第205頁第206頁第207頁第208頁第209頁第210頁第211頁第212頁第213頁第214頁第215頁第216頁第217頁第218頁第219頁第220頁

103

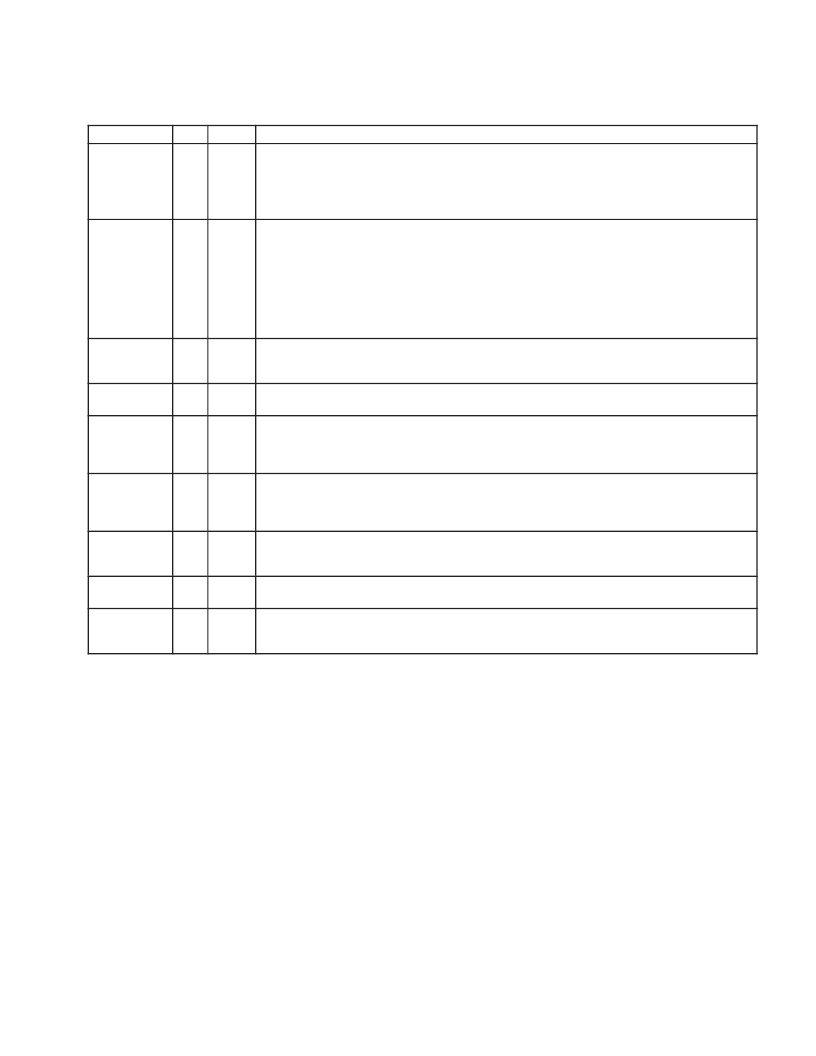

Table 102. Base Register Field Descriptions (Continued)

FIELD

SIZE

TYPE

DESCRIPTION

ISBR

1

R/W

Initiate short arbitrated bus reset. This bit, if set to 1, instructs the PHY layer to initiate a short (1.3

μ

s)

arbitrated bus reset at the next opportunity. This bit is cleared to 0 by a bus reset.

NOTE: Legacy IEEE Std 1394-1995 compliant PHY layers can not be capable of performing short bus

resets. Therefore, initiation of a short bus reset in a network that contains such a legacy device results in a

long bus reset being performed.

Loop

1

R/W

Loop detect. This bit is set to 1 when the arbitration controller times out during tree-ID start and may indicate

that the bus is configured in a loop. This bit is cleared to 0 by system (hardware) reset or by writing a 1 to this

register bit.

If the loop and watchdog bits are both set and the LLC is or becomes inactive, the PHY layer activates the

LLC to service the interrupt.

NOTE: If the network is configured in a loop, only those nodes which are part of the loop generate a

configuration-timeout interrupt. All other nodes instead time out waiting for the tree-ID and/or self-ID process

to complete and then generate a state time-out interrupt and bus-reset.

Pwr_fail

1

R/W

Cable power failure detect. This bit is set to 1 whenever the CPS input transitions from high to low indicating

that cable power may be too low for reliable operation. This bit is cleared to 0 by system (hardware) reset or

by writing a 1 to this register bit.

Timeout

1

R/W

State time-out interrupt. This bit indicates that a state time-out has occurred (which also causes a bus reset

to occur). This bit is cleared to 0 by system (hardware) reset or by writing a 1 to this register bit.

Port_event

1

R/W

Port event detect. This bit is set to 1 upon a change in the bias (unless disabled) connected, disabled, or fault

bits for any port for which the port interrupt enable (Int_enable) bit is set. Additionally, if the watchdog bit is

set, the Port_event bit is set to 1 at the start of resume operations on any port. This bit is cleared to 0 by

system (hardware) reset or by writing a 1 to this register bit.

Enab_accel

1

R/W

Enable accelerated arbitration. This bit enables the PHY layer to perform the various arbitration acceleration

enhancements defined in IEEE Std 1394a-2000 (ACK-accelerated arbitration, asynchronous fly-by

concatenation, and isochronous fly-by concatenation). This bit is cleared to 0 by system (hardware) reset

and is unaffected by bus reset.

Enab_multi

1

R/W

Enable multispeed concatenated packets. This bit enables the PHY layer to transmit concatenated packets

of differing speeds in accordance with the protocols defined in IEEE Std 1394a-2000. This bit is cleared to 0

by system (hardware) reset and is unaffected by bus reset.

Page_Select

3

R/W

Page_Select. This field selects the register page to use when accessing register addresses 8 through 15.

This field is cleared to 0 by a system (hardware) reset and is unaffected by bus reset.

Port_Select

4

R/W

Port_Select. This field selects the port when accessing per-port status or control (for example, when one of

the port status/control registers is accessed in page 0). Ports are numbered starting at 0. This field is cleared

to 0 by system (hardware) reset and is unaffected by bus reset.

相關PDF資料 |

PDF描述 |

|---|---|

| PCI4515 | SINGLE SOCKET CARDBUS CONTROLLER WITH INTEGRATED |

| PCI4515GHK | SINGLE SOCKET CARDBUS CONTROLLER WITH INTEGRATED |

| PCI4515ZHK | SINGLE SOCKET CARDBUS CONTROLLER WITH INTEGRATED |

| PCI6420 | Integrated 2-Slot PC Card & Dedicated Flash Media Controller |

| PCI6421 | DUAL/SINGLE SOCKET CARDBUS AND ULTRAMEDIA CONTROLLER |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| PCI4510RGVF | 功能描述:外圍驅(qū)動器與原件 - PCI Card & Integrated 1394a-2000 OHCI RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

| PCI4510RZVF | 功能描述:外圍驅(qū)動器與原件 - PCI Card & Integrated 1394a-2000 OHCI RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

| PCI4510ZHK | 制造商:Texas Instruments 功能描述: |

| PCI4512ZHK | 功能描述:外圍驅(qū)動器與原件 - PCI Integ sngl-socket PC Card controller RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

| PCI4515 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:SINGLE SOCKET CARDBUS CONTROLLER WITH INTEGRATED |

發(fā)布緊急采購,3分鐘左右您將得到回復。