- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄378045 > PCI4510PDV (Texas Instruments, Inc.) PC CARD AND INTEGRATED 1394A-2000 OHCI TWO PORT PHY/LINK LAYER CONTROLLER PDF資料下載

參數(shù)資料

| 型號: | PCI4510PDV |

| 廠商: | Texas Instruments, Inc. |

| 英文描述: | PC CARD AND INTEGRATED 1394A-2000 OHCI TWO PORT PHY/LINK LAYER CONTROLLER |

| 中文描述: | PC卡和綜合1394A端口- 2000 OHCI的兩個端口物理層/鏈路層控制器 |

| 文件頁數(shù): | 104/220頁 |

| 文件大小: | 1356K |

| 代理商: | PCI4510PDV |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁當前第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁第162頁第163頁第164頁第165頁第166頁第167頁第168頁第169頁第170頁第171頁第172頁第173頁第174頁第175頁第176頁第177頁第178頁第179頁第180頁第181頁第182頁第183頁第184頁第185頁第186頁第187頁第188頁第189頁第190頁第191頁第192頁第193頁第194頁第195頁第196頁第197頁第198頁第199頁第200頁第201頁第202頁第203頁第204頁第205頁第206頁第207頁第208頁第209頁第210頁第211頁第212頁第213頁第214頁第215頁第216頁第217頁第218頁第219頁第220頁

432

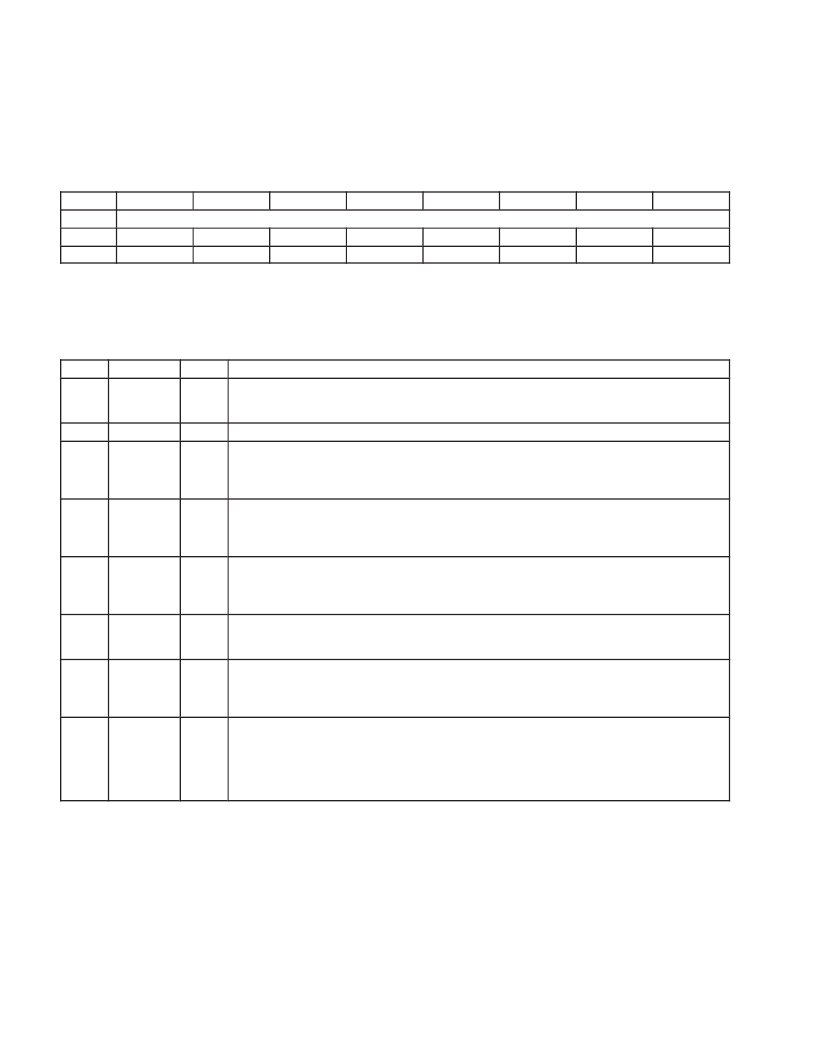

4.47 Serial Bus Control and Status Register

The serial bus control and status register communicates serial bus status information and selects the quick command

protocol. Bit 5 (REQBUSY) in this register must be polled during serial bus byte reads to indicate when data is valid

in the serial bus data register. See Table 425 for a complete description of the register contents.

Bit

7

6

5

4

3

2

1

0

Name

Serial bus control and status

Type

RW

R

R

R

RW

RW

RC

RC

Default

0

0

0

0

0

0

0

0

Register:

Offset:

Type:

Default:

Serial bus control and status

B3h (Function 0)

Read-only, Read/Write, Read/Clear

00h

Table 425. Serial Bus Control and Status Register Description

BIT

SIGNAL

TYPE

FUNCTION

7

PROT_SEL

RW

Protocol select. When bit 7 is set, the send-byte protocol is used on write requests and the receive-byte

protocol is used on read commands. The word address byte in the serial bus index register (see

Section 4.45) is not output by the PCI4510 device when bit 7 is set.

6

RSVD

R

Reserved. Bit 6 returns 0 when read.

5

REQBUSY

R

Requested serial bus access busy. Bit 5 indicates that a requested serial bus access (byte read or write)

is in progress. A request is made, and bit 5 is set, by writing to the serial bus slave address register (see

Section 4.46). Bit 5 must be polled on reads from the serial interface. After the byte read access has been

requested, the read data is valid in the serial bus data register.

4

ROMBUSY

R

Serial ROM busy status. Bit 4 indicates the status of the PCI4510 serial ROM circuitry. Bit 4 is set during

the loading of the subsystem ID and other default values from the serial bus ROM.

0 = Serial ROM circuitry is not busy

1 = Serial ROM circuitry is busy

3

SBDETECT

RW

Serial bus detect. When bit 3 is set, it indicates that the serial bus interface is detected through a pullup

resistor on the SCL terminal after reset.

0 = Serial bus interface not detected

1 = Serial bus interface detected

2

SBTEST

RW

Serial bus test. When bit 2 is set, the serial bus clock frequency is increased for test purposes.

0 = Serial bus clock at normal operating frequency,

1 = Serial bus clock frequency increased for test purposes

100 kHz (default)

1

REQ_ERR

RC

Requested serial bus access error. Bit 1 indicates when a data error occurs on the serial interface during

a requested cycle and may be set due to a missing acknowledge. Bit 1 is cleared by a writeback of 1.

0 = No error detected during user requested byte read or write cycle

1 = Data error detected during user requested byte read or write cycle

0

ROM_ERR

RC

ROM data error status. Bit 0 indicates when a data error occurs on the serial interface during the auto-load

from the serial bus ROM and may be set due to a missing acknowledge. Bit 0 is also set on invalid ROM

data formats. See Section 3.6.3,

Serial Bus EEPROM Application

, for details on ROM data format. Bit 0 is

cleared by a writeback of 1.

0 = No error detected during auto-load from serial bus ROM

1 = Data error detected during auto-load from serial bus ROM

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PCI4515 | SINGLE SOCKET CARDBUS CONTROLLER WITH INTEGRATED |

| PCI4515GHK | SINGLE SOCKET CARDBUS CONTROLLER WITH INTEGRATED |

| PCI4515ZHK | SINGLE SOCKET CARDBUS CONTROLLER WITH INTEGRATED |

| PCI6420 | Integrated 2-Slot PC Card & Dedicated Flash Media Controller |

| PCI6421 | DUAL/SINGLE SOCKET CARDBUS AND ULTRAMEDIA CONTROLLER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PCI4510RGVF | 功能描述:外圍驅(qū)動器與原件 - PCI Card & Integrated 1394a-2000 OHCI RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

| PCI4510RZVF | 功能描述:外圍驅(qū)動器與原件 - PCI Card & Integrated 1394a-2000 OHCI RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

| PCI4510ZHK | 制造商:Texas Instruments 功能描述: |

| PCI4512ZHK | 功能描述:外圍驅(qū)動器與原件 - PCI Integ sngl-socket PC Card controller RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

| PCI4515 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:SINGLE SOCKET CARDBUS CONTROLLER WITH INTEGRATED |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。