- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄367816 > PCF50732 (NXP Semiconductors N.V.) Baseband and audio interface for GSM PDF資料下載

參數(shù)資料

| 型號(hào): | PCF50732 |

| 廠商: | NXP Semiconductors N.V. |

| 英文描述: | Baseband and audio interface for GSM |

| 中文描述: | 用于GSM基帶和音頻接口 |

| 文件頁(yè)數(shù): | 52/64頁(yè) |

| 文件大小: | 322K |

| 代理商: | PCF50732 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)當(dāng)前第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)

1999 May 03

52

Philips Semiconductors

Objective specification

Baseband and audio interface for GSM

PCF50732

18.5

V

DDA

= 2.5 to 2.75 V; T

amb

=

40 to +85

°

C.

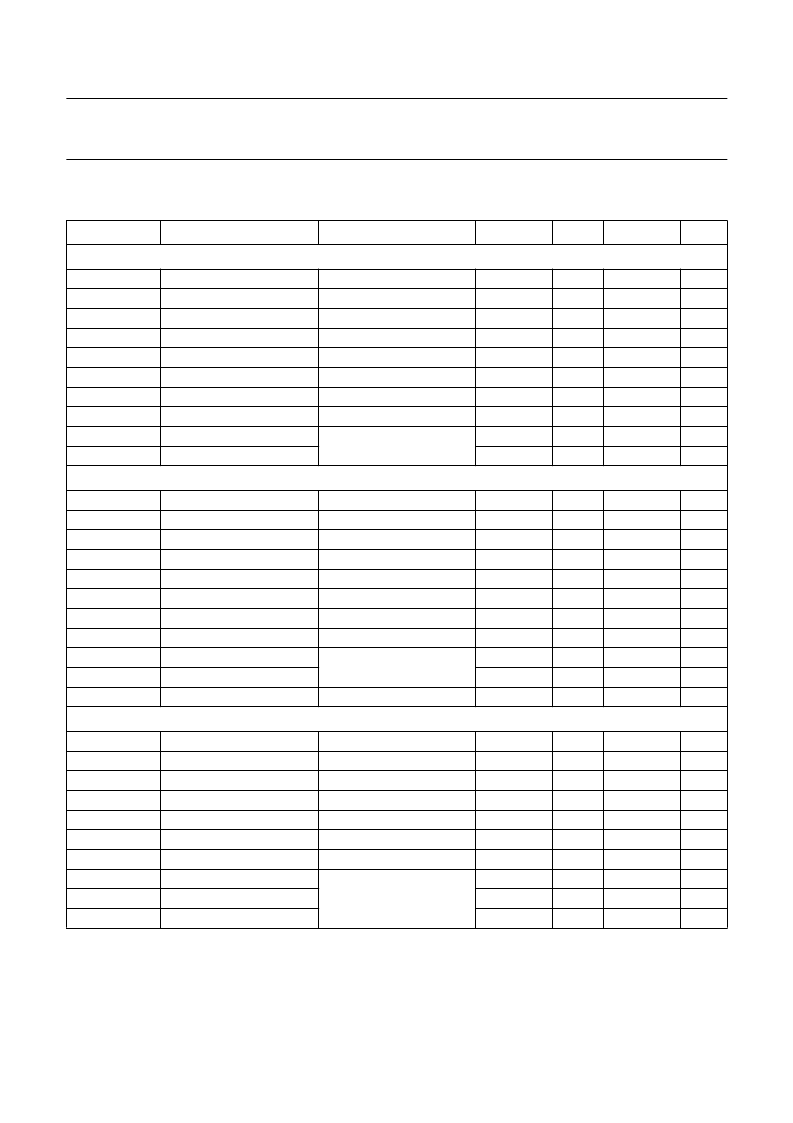

Auxiliary digital-to-analog converters

Notes

1.

2.

INL: the difference of the output to the best fit line. INL

(i)

= [V

(i)

(a + i

×

b)]/1 LSB; INL = (INL

(i)(max)

INL

(i)(min)

)/2.

DNL is the difference between individual code width and average code width (1 LSB); maximum and minimum

specified. DNL

(i)

= [(V

(i + 1)

V

(i)

1 LSB)/1 LSB]; DNL

(min)

>

1 is equivalent to monotonicity V

(i + 1)

> V

(i)

.

SYMBOL

PARAMETER

CONDITIONS

MIN.

TYP.

MAX.

UNIT

AUXDAC1

RES

DAC1

VOMIN

DAC1

VOMAX

DAC1

VDEF

DAC1

MON

DAC1

INL

DAC1

DNL

DAC1

OFFS

DAC1

FSST

DAC1

LSBST

DAC1

resolution

minimum output voltage

maximum output voltage

output voltage after reset

monotonicity range

integral non-linearity

(1)

differential non-linearity

(2)

offset error

full-scale settling time

one LSB settling time

0

2.1

5.0

1.0

80

8

2.2

1.147

8

40

8

0.15

2.3

+5.0

+1.0

+80

bit

V

V

V

bit

LSB

LSB

mV

μ

s

μ

s

register value: 000H

register value: 0FFH

register value: 085H

load: 50 pF // 2 k

,

to V

SS

;

see Fig.13a

AUXDAC2

RES

DAC2

VOMIN

DAC2

VOMAX

DAC2

VDEF

DAC2

MON

DAC2

INL

DAC2

DNL

DAC2

OFFS

DAC2

FSST

DAC2

LSBST

DAC2

POST

DAC2

resolution

minimum output voltage

maximum output voltage

output voltage after reset

monotonicity range

integral non-linearity

(1)

differential non-linearity

(2)

offset error

full-scale settling time

one LSB settling time

power-on settling time

0

2.1

1.0

25

12

2.2

1.1

12

±

10

40

8

0.15

2.32

+2.0

+25

4

bit

V

V

V

bit

LSB

LSB

mV

μ

s

μ

s

ms

register value: 000H

register value: FFFH

register value: 800H

load: 50 pF // 10 k

,

to

V

SS

; see Fig.13b

see Section 18.1

AUXDAC3

RES

DAC3

VOMIN

DAC3

VOMAX

DAC3

MON

DAC3

INL

DAC3

DNL

DAC3

OFFS

DAC3

FSST

DAC3

LSBST

DAC3

SSC

DAC3

resolution

minimum output voltage

maximum output voltage

monotonicity range

integral non-linearity

(1)

differential non-linearity

(2)

offset error

full-scale settling time

one LSB settling time

output source/sink current

0

2.1

5.0

1.0

40

1

10

2.2

10

10

2.5

0.15

2.3

+5.0

+1.0

+40

15

2.5

bit

V

V

bit

LSB

LSB

mV

μ

s

μ

s

mA

register value: 000H

register value: 3FFH

load: 50 pF // 1 k

,

to V

SS

;

see Fig.13c

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PCF50732H | Baseband and audio interface for GSM |

| PCF7991AT | Advanced Basestation IC, ABIC |

| PCF80C31BH4-24H | CMOS single-chip 8-bit microcontrollers |

| PCB80C51BH-2H | CMOS single-chip 8-bit microcontrollers |

| PCB80C51BH-2P | CMOS single-chip 8-bit microcontrollers |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PCF50732H | 制造商:PHILIPS 制造商全稱(chēng):NXP Semiconductors 功能描述:Baseband and audio interface for GSM |

| PCF5075 | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:Power Control/Management |

| PCF5075TDK-T | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:Power Control/Management |

| PCF5077T | 制造商:PHILIPS 制造商全稱(chēng):NXP Semiconductors 功能描述:Power amplifier controller for GSM and PCN systems |

| PCF5078 | 制造商:PHILIPS 制造商全稱(chēng):NXP Semiconductors 功能描述:Power amplifier controller for GSM and PCN systems |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。