- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄367816 > PCF50732 (NXP Semiconductors N.V.) Baseband and audio interface for GSM PDF資料下載

參數(shù)資料

| 型號(hào): | PCF50732 |

| 廠商: | NXP Semiconductors N.V. |

| 英文描述: | Baseband and audio interface for GSM |

| 中文描述: | 用于GSM基帶和音頻接口 |

| 文件頁數(shù): | 11/64頁 |

| 文件大?。?/td> | 322K |

| 代理商: | PCF50732 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁當(dāng)前第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁

1999 May 03

11

Philips Semiconductors

Objective specification

Baseband and audio interface for GSM

PCF50732

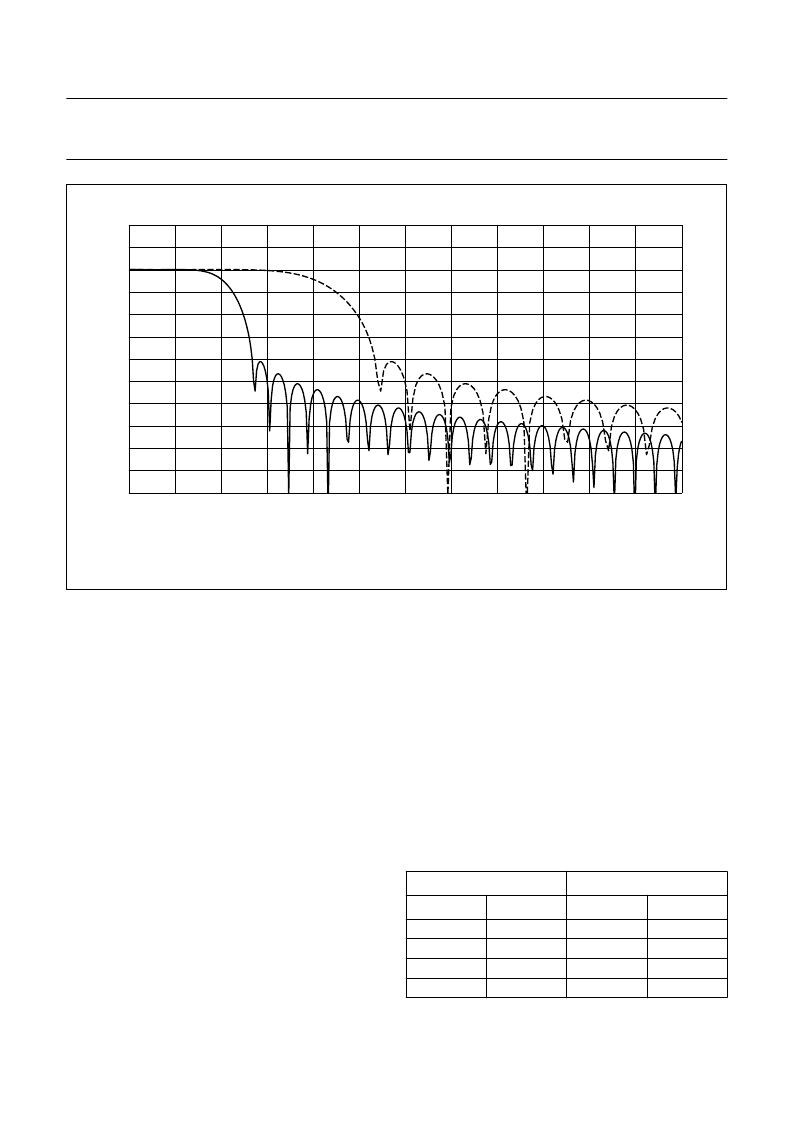

Fig.3 Transfer functions for the baseband receive filter.

3

handbook, full pagewidth

gain

(dB)

600

500

f (kHz)

0

100

200

300

400

20

40

60

80

100

0

MBL025

NZIF

9.3

Baseband Serial Interface (BSI)

9.3.1

O

VERVIEW

The digital part of the baseband consists of a receive

section and a transmit section. The receive section is a

FIR filter that reduces the 6.5 MHz (13 MHz for

NZIF mode) bitstream from the sigma-delta converters

into 2

×

12-bit values at 270.833 kHz (541.667 kHz for

NZIF mode).

The transmit section converts the 270.833 kHz data

stream from the DSP into a GMSK signal sampled at

4.333 MHz. The 10-bit I and Q signals are then fed into

two 10-bit DACs. The power ramping signal is also

generated by the transmit section with the 10-bit

AUXDAC3 block.

9.3.2

T

RANSMIT PATH BLOCK DESCRIPTION

9.3.2.1

Transmit serial interface

The power-up of the BSI transmit path is controlled via the

TXON pin. When TXON is pulled HIGH, the transmit path

recovers from power-down. The MCLK/48 = 270.833 kHz

output signal BIOCLK is activated. When the BIEN0 period

has elapsed the output signal BIEN goes LOW and the bits

to be transmitted are clocked out of the DSP.

BIEN0 must be at least 10 quarterbits long to allow settling

of the analog filters. Bits are clocked out of the DSP by the

falling edge and clocked into the PCF50732 by the rising

edge of BIOCLK. After the BIEN1 period has elapsed,

BIEN is set HIGH again and transmission from the DSP

ends. Logic 1s are modulated whenever BIEN is HIGH

and the baseband transmit (BBTX) block is active. Values

for BIEN0 and BIEN1 can be set in the Burst control

register.

Figure 5 shows the timing for the BSI data transmission.

In power-down the de-asserted value of BIOCLK is high-Z

and BIEN is HIGH. Typical connection to the system DSP

is defined in Table 1.

Table 1

Connection of BSI transmit signals to

PCF5087X

PCF50732

PCF5087X

PIN

I/O

PIN

I/O

TXON

BDIO

BIEN

BIOCLK

I

RFSIG[y]

SIOXD

SOXEN_N

SIOXCLK

O

I/O

I

I

I/O

O

O

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PCF50732H | Baseband and audio interface for GSM |

| PCF7991AT | Advanced Basestation IC, ABIC |

| PCF80C31BH4-24H | CMOS single-chip 8-bit microcontrollers |

| PCB80C51BH-2H | CMOS single-chip 8-bit microcontrollers |

| PCB80C51BH-2P | CMOS single-chip 8-bit microcontrollers |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PCF50732H | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Baseband and audio interface for GSM |

| PCF5075 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Power Control/Management |

| PCF5075TDK-T | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Power Control/Management |

| PCF5077T | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Power amplifier controller for GSM and PCN systems |

| PCF5078 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Power amplifier controller for GSM and PCN systems |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。