- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369944 > P89C738 (NXP Semiconductors N.V.) 8-bit Flash microcontrollers PDF資料下載

參數(shù)資料

| 型號: | P89C738 |

| 廠商: | NXP Semiconductors N.V. |

| 英文描述: | 8-bit Flash microcontrollers |

| 中文描述: | 8位閃存微控制器 |

| 文件頁數(shù): | 30/64頁 |

| 文件大小: | 360K |

| 代理商: | P89C738 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁當前第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁

1998 Apr 07

30

Philips Semiconductors

Product specification

8-bit Flash microcontrollers

P89C738; P89C739

13.4

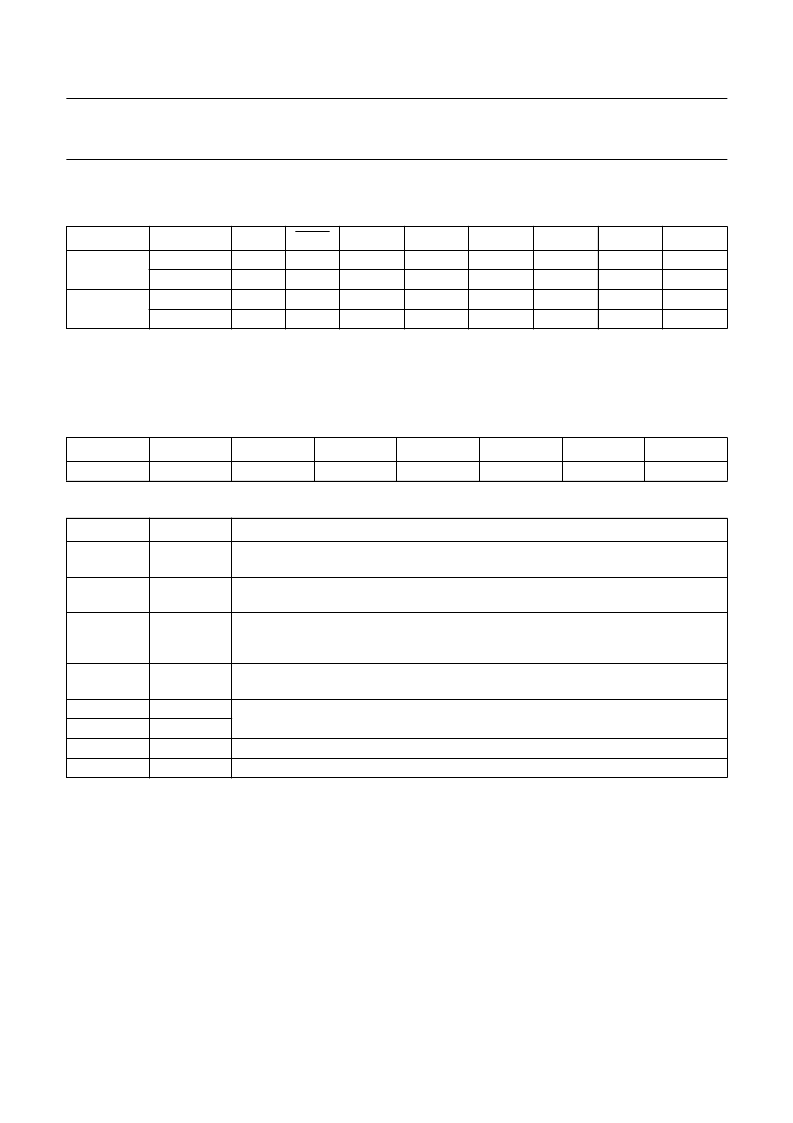

Status of external pins

Table 20

Status of the external pins during Idle and Power-down modes

13.5

Power Control Register (PCON)

Special modes are activated by software via the SFR PCON. PCON is not bit addressable. The reset value of PCON is

00H.

Table 21

Power Control Register (SFR address 87H)

Table 22

Description of PCON bits

Note

1.

If logic 1s are written to PD and IDL at the same time, PD takes precedence.

MODE

MEMORY

ALE

PSEN

PORT 0

PORT 1

PORT 2

PORT 3

PORT 4

PORT 5

Idle

internal

external

internal

external

HIGH

HIGH

LOW

LOW

HIGH

HIGH

LOW

LOW

port data

floating

port data

floating

port data

port data

port data

port data

port data

address

port data

port data

port data

port data

port data

port data

port data

port data

port data

port data

port data

port data

port data

port data

Power-down

7

6

5

4

3

2

1

0

SMOD

ARE

RFI

WLE

GF1

GF0

PD

IDL

BIT

SYMBOL

DESCRIPTION

7

SMOD

Double baud rate bit

. When set to a logic 1 the baud rate is doubled when Timer 1 is

used to generate baud rate, and the Serial Port is used in Modes 1, 2 or 3.

AUX-RAM enable bit.

When set to a logic 1 the AUX-RAM is disabled, so that all

MOVX-instructions access the external data memory.

Reduced Radio Frequency Interference bit

. When set to a logic 1 the toggling of the

ALE pin is prohibited. This bit is cleared on reset. See also Chapters 1 “Features”: on

EMC and 6 “Pinning information”: note 2.

Watchdog Load Enable

. This flag must be set by software prior to loading the

Watchdog Timer (T3). It is cleared when timer T3 is loaded.

General-purpose flag bit

.

6

ARE

5

RFI

4

WLE

3

2

1

0

GF1

GF0

PD

(1)

IDL

(1)

Power-down select.

Setting this bit activates the Power-down mode.

Idle mode select.

Setting this bit activates the Idle mode.

相關PDF資料 |

PDF描述 |

|---|---|

| P89C739ABA | 8-bit Flash microcontrollers |

| P89C739ABB | 8-bit Flash microcontrollers |

| P89C738ABA | 8-bit Flash microcontrollers |

| P89C738ABB | 8-bit Flash microcontrollers |

| P89C738ABP | 8-bit Flash microcontrollers |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| P89C738ABA | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:8-bit Flash microcontrollers |

| P89C738ABB | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:8-bit Flash microcontrollers |

| P89C738ABP | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:8-bit Flash microcontrollers |

| P89C738BBB | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:8-Bit Microcontroller |

| P89C739 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:8-bit Flash microcontrollers |

發(fā)布緊急采購,3分鐘左右您將得到回復。