- 您現在的位置:買賣IC網 > PDF目錄369939 > P28F001BX-T70 (INTEL CORP) 1-MBIT (128K x 8) BOOT BLOCK FLASH MEMORY PDF資料下載

參數資料

| 型號: | P28F001BX-T70 |

| 廠商: | INTEL CORP |

| 元件分類: | PROM |

| 英文描述: | 1-MBIT (128K x 8) BOOT BLOCK FLASH MEMORY |

| 中文描述: | 128K X 8 FLASH 12V PROM, 70 ns, PDIP32 |

| 封裝: | 0.620 X 1.640 INCH, PLASTIC, DIP-32 |

| 文件頁數: | 24/33頁 |

| 文件大?。?/td> | 436K |

| 代理商: | P28F001BX-T70 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁當前第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁

28F001BX-T/28F001BX-B

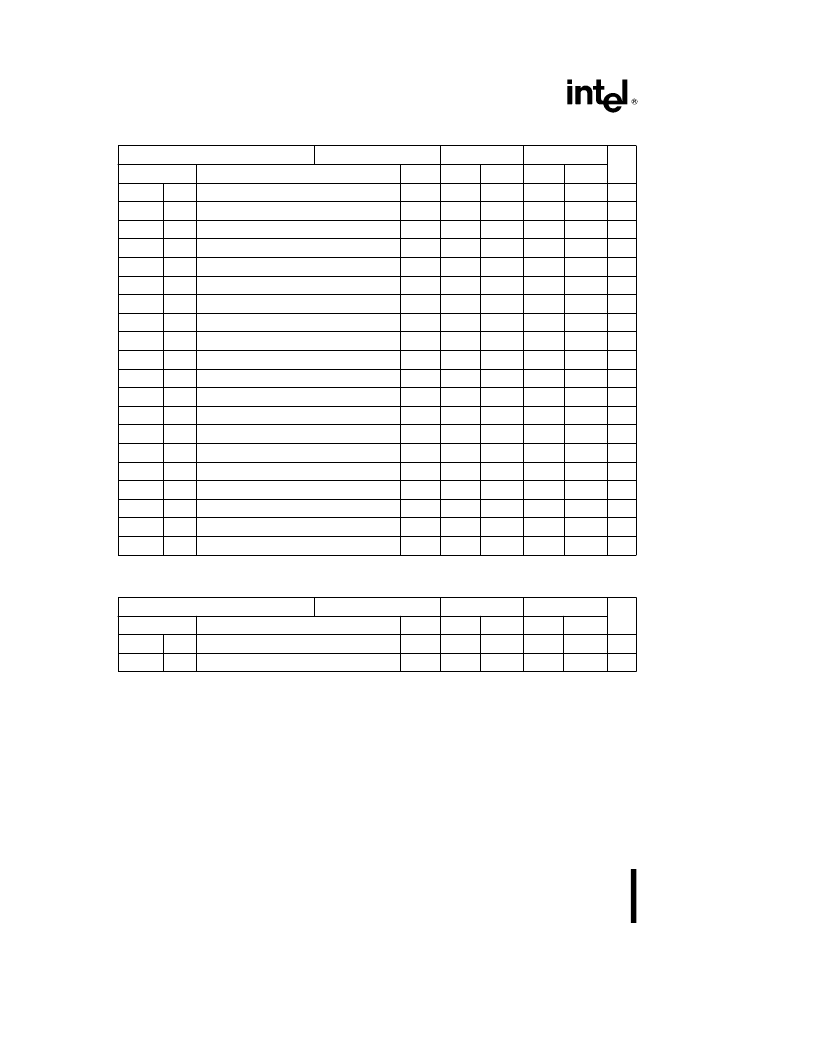

AC CHARACTERISTICSDWrite/Erase/Program Operations

(1, 9)

Versions

V

CC

g

10%

(10)

28F001BX-120

28F001BX-150

Unit

Symbol

Parameter

Notes

Min

Max

Min

Max

t

AVAV

t

WC

Write Cycle Time

120

150

ns

t

PHWL

t

PS

RP

Y

High Recovery to WE

Y

Going Low

2

480

480

ns

t

ELWL

t

CS

CE

Y

Setup to WE

Y

Going Low

10

10

ns

t

WLWH

t

WP

WE

Y

Pulse Width

50

50

ns

t

PHHWH

t

PHS

RP

Y

V

HH

Setup to WE

Y

Going High

V

PP

Setup to WE

Y

Going High

Address Setup to WE

Y

Going High

2

100

100

ns

t

VPWH

t

VPS

2

100

100

ns

t

AVWH

t

AS

3

50

50

ns

t

DVWH

t

DS

Data Setup to WE

Y

Going High

4

50

50

ns

t

WHDX

t

DH

Data Hold from WE

Y

High

10

10

ns

t

WHAX

t

AH

Address Hold from WE

Y

High

10

10

ns

t

WHEH

t

CH

t

WPH

WE

Y

Pulse Width High

CE

Y

Hold from WE

Y

High

10

10

ns

t

WHWL

50

50

ns

t

WHQV1

Duration of Programming Operation

5, 6, 7

15

15

m

s

t

WHQV2

Duration of Erase Operation (Boot)

5, 6, 7

1.3

1.3

sec

t

WHQV3

Duration of Erase Operation (Parameter)

5, 6, 7

1.3

1.3

sec

t

WHQV4

Duration of Erase Operation (Main)

5, 6, 7

3.0

3.0

sec

t

WHGL

Write Recovery before Read

0

0

m

s

t

QVVL

t

VPH

V

PP

Hold from Valid SRD

RP

Y

V

HH

Hold from Valid SRD

2, 6

0

0

ns

t

QVPH

t

PHH

2, 7

0

0

ns

t

PHBR

Boot-Block Relock Delay

2

100

100

ns

PROM Programmer Specifications

Versions

V

CC

g

10%

28F001BX-120

28F001BX-150

Unit

Symbol

Parameter

Notes

Min

Max

Min

Max

t

GHHWL

OE

Y

V

HH

Setup to WE

Y

Going Low

OE

Y

V

HH

Hold from WE

Y

High

2, 8

480

480

ns

t

WHGH

2, 8

480

480

ns

NOTES:

1. Read timing characteristics during erase and program operations are the same as during read-only operations. Refer to

AC Characteristics for Read-Only Operations.

2. Sampled, not 100% tested.

3. Refer to Table 3 for valid A

IN

for byte programming or block erasure.

4. Refer to Table 3 for valid D

IN

for byte programming or block erasure.

5. The on-chip Write State Machine incorporates all program and erase system functions and overhead of standard Intel

Flash Memory, including byte program and verify (programming) and block precondition, precondition verify, erase and erase

verify (erasing).

6. Program and erase durations are measured to completion (SR.7

e

1). V

PP

should be held at V

PPH

until determination of

program/erase success (SR.3/4/5

e

0).

7. For boot block programming and erasure, RP

Y

should be held at V

HH

until determination of program/erase success

(SR.3/4/5

e

0).

8. Alternate boot block access method.

9. Erase/Program Cycles on extended temperature products is 10,000 cycles.

10. See standard test configuration.

24

相關PDF資料 |

PDF描述 |

|---|---|

| P28F001BX-T90 | 1-MBIT (128K x 8) BOOT BLOCK FLASH MEMORY |

| P28F001BX-B120 | 1-MBIT (128K x 8) BOOT BLOCK FLASH MEMORY |

| P28F001BX-B150 | 1-MBIT (128K x 8) BOOT BLOCK FLASH MEMORY |

| P28F001BX-B70 | 1-MBIT (128K x 8) BOOT BLOCK FLASH MEMORY |

| P28F001BX-B90 | DB9 MALE TO DB9 FEMALE AME |

相關代理商/技術參數 |

參數描述 |

|---|---|

| P28F001BX-T90 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:1-MBIT (128K x 8) BOOT BLOCK FLASH MEMORY |

| P28F002BC-T120 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:28F002BC 2-MBIT (256K X 8) BOOT BLOCK FLASH MEMORY |

| P28F002BC-T80 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:28F002BC 2-MBIT (256K X 8) BOOT BLOCK FLASH MEMORY |

| P28F010120 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| P28F010-120 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:28F010 1024K (128K X 8) CMOS FLASH MEMORY |

發(fā)布緊急采購,3分鐘左右您將得到回復。