- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369937 > P1602Z solid state crowbar devices PDF資料下載

參數(shù)資料

| 型號: | P1602Z |

| 英文描述: | solid state crowbar devices |

| 中文描述: | 固態(tài)撬棍設(shè)備 |

| 文件頁數(shù): | 181/212頁 |

| 文件大?。?/td> | 1877K |

| 代理商: | P1602Z |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁第162頁第163頁第164頁第165頁第166頁第167頁第168頁第169頁第170頁第171頁第172頁第173頁第174頁第175頁第176頁第177頁第178頁第179頁第180頁當(dāng)前第181頁第182頁第183頁第184頁第185頁第186頁第187頁第188頁第189頁第190頁第191頁第192頁第193頁第194頁第195頁第196頁第197頁第198頁第199頁第200頁第201頁第202頁第203頁第204頁第205頁第206頁第207頁第208頁第209頁第210頁第211頁第212頁

PCB Layout

2002 Teccor Electronics

SIDACtor

Data Book and Design Guide

5 - 19

http://www.teccor.com

+1 972-580-7777

T

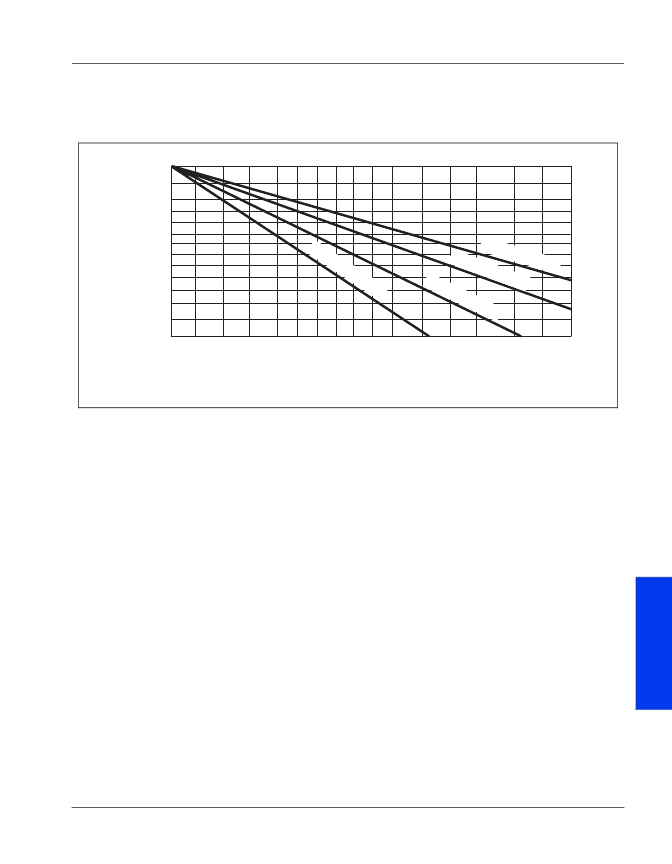

has been done, Figure 5.5 shows the conversion of the cross-sectional area to the required

conductor width, dependent on the copper foil thickness of the trace.

Figure 5.5

Conductor Width versus Area

Trace Separation

Tip and Ring traces are subjected to various transient and overvoltage conditions. To

prevent arcing between traces, minimum trace separation should be maintained. UL 60950

will provide additional information regarding creepage and clearance requirements, which

are dependent on the Comparative Tracking Index (CTI) rating of the PCB, working voltage,

and the expected operating environment. See "UL 60950 3rd Edition (formerly UL 1950, 3rd

edition)" on page 4-16 of this data book.

A good rule of thumb for outside layers is to maintain a minimum of 18 mils for 1kV isolation.

Route the Tip and Ring traces towards the edge of the PCB away from areas containing

static sensitive devices.

Grounding

Although often overlooked, grounding is a very important design consideration when laying

out a protection interface circuit. To optimize its effectiveness, several things should be

considered in sequence:

1. Provide a large copper plane with a grid pattern for the Ground reference point.

2. Decide if a single-point or a multi-point grounding scheme is to be used. A single-point

(also called centralized) grounding scheme is used for circuit dimensions smaller than

one-tenth of a wavelength ( = 300,000/frequency) and a multi-point (distributed)

grounding scheme is used for circuit trace lengths greater than one-fourth of a

wavelength.

.350

.300

.250

.030

.050

.070

.100

.150

.200

.010

.020

.005

.001

0

1

10

20

100 150

300

400

500

600

700

Conductor Cross-Section Area (sq mils)

5

30 50 70

200

250

C

0

(1 oz/ft2 0.0014"

(12ozf2 00007"

(2 oz/ft2) 0.0028"

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| P1803A | solid state crowbar devices |

| P1803ACMC | solid state crowbar devices |

| P1803U | solid state crowbar devices |

| P1803Z | solid state crowbar devices |

| P197 | POWER PUSHBUTTON SERIES |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| P1603 | 制造商:Pulse 功能描述:- Bulk |

| P160-331FS | 制造商:API Delevan 功能描述:POWER MICRO I CHIP INDUCTOR SURFACE MOUNT POWER INDUCTOR, 0. - Bulk |

| P160-331FS BULK 50 | 制造商:API Delevan 功能描述:INDUCTOR .33 UH 1% SMD |

| P160-331GS | 制造商:API Delevan 功能描述:POWER MICRO I CHIP INDUCTOR SURFACE MOUNT POWER INDUCTOR, 0. - Bulk |

| P160-331GS BULK 50 | 制造商:API Delevan 功能描述:INDUCTOR .33 UH 2% SMD |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。