- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376214 > MX98725 (Electronic Theatre Controls, Inc.) SINGLE CHIP FAST ETHERNET NIC CONTROLLER PDF資料下載

參數(shù)資料

| 型號(hào): | MX98725 |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | SINGLE CHIP FAST ETHERNET NIC CONTROLLER |

| 中文描述: | 單晶片快速以太網(wǎng)卡控制器 |

| 文件頁(yè)數(shù): | 20/33頁(yè) |

| 文件大小: | 177K |

| 代理商: | MX98725 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)當(dāng)前第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)

20

P/N:PM0488

REV. 1.7, SEP. 15, 1998

MX98725

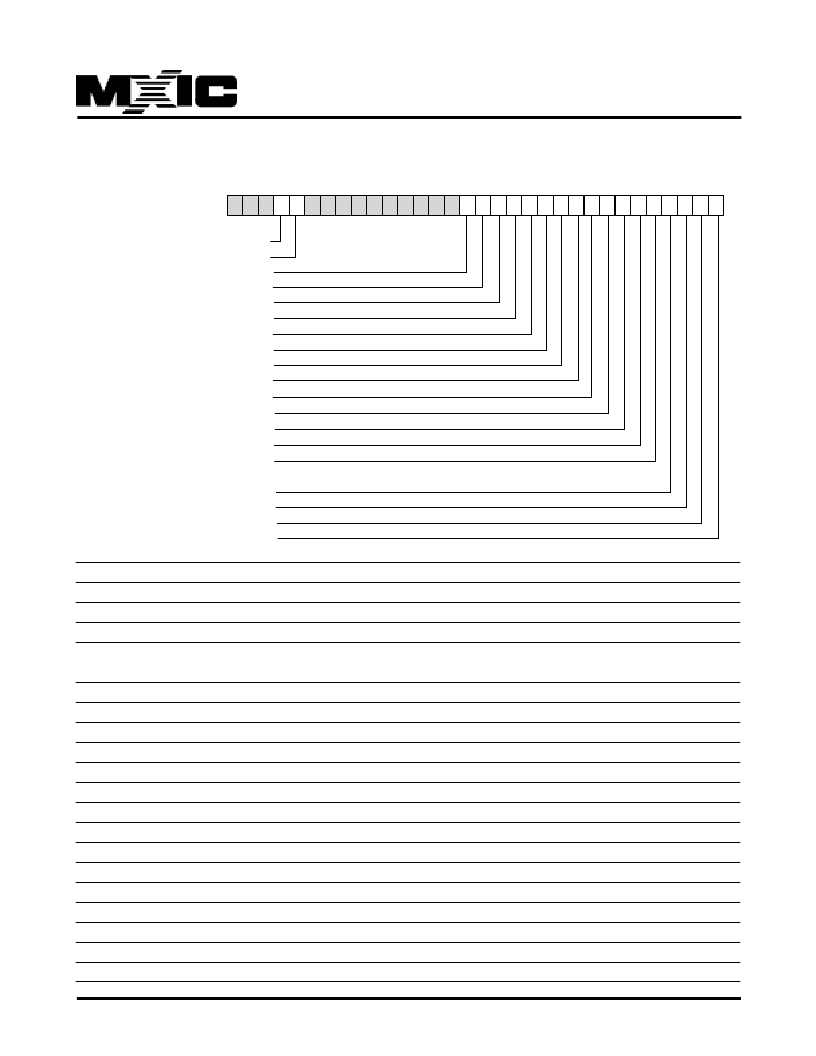

5.2.7 INTERRUPT MASK REGISTER ( CSR7 )

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

NIE-Normal interrupt Summary Enable

AIE-Abnormal Interrupt Summary Enable

ERIE-Early Receive Interrupt Enable

FBE-Fatal Bus Error Enable

LFE-Link Fail Enable

GPTE-General-Purpose Timer Enable

ETIE-Early Transmit Interrupt Enable

RWE-Receive Watchdog Enable

RSE-Receive Stopped Enable

RUE-Receive Buffer Unavailable Enable

RIE-Receive Interrupt Enable

UNE-Underflow Interrupt Enable

LPANCIE-Link Pass

/Nway Complete Interrupt Enable

TJE-Transmit Jabber Timeout Enable

TUE-Transmit Buffer Unavailable Enable

TSE-Transmit Stopped Enable

TIE-Transmit Interrupt Enable

LCE-Link Changed Enable

MPIE-Magic Packet Interrupt Enable

Field

28

27

16

15

Name

MPIE

LCE

NIE

AIE

Description

Magic Packet Interrupt Enable, enables CSR5<28>.

Link Changed Enable, enables CSR5<27>.

Normal Interrupt Summary Enable, set to enable CSR5<0>, CSR5<2>, CSR5<6>.

Abnormal Interrupt Summary enable, set to enbale CSR5<1>, CSR5<3>, CSR5<5>,

CSR5<7>, CSR5<8>, CSR5<9>, CSR5<11> and CSR5<13>.

Early Receive Interrupt Enable

Fatal Bus Error Enable, set together with with CSR7<15> enables CSR5<13>.

Link Fail Interrupt Enable, enables CSR5<12>

General_-Purpose Timer Enable, set together with CSr7<15> enables CSR5<11>.

Early Transmit Interrupt Enable, enables CSR5<10>

Receive Watchdog Timeout Enable, set together with CSR7<15> enables CSR5<9>.

Receive Stopped Enable, set together with CSR7<15> enables CSR5<8>.

Receive Buffer Unavailable Enable, set together with CSR7<15> enables CSR5<7>.

Receive Interrupt Enable, set together with CSR7<16> enables CSR5<6>.

Underflow Interrupt Enable, set together with CSR7<15> enables CSR5<5>.

Link Pass/Autonegotiation Completed Interrupt Enable

Transmit Jabber Timeout Enable, set together with CSR7<15> enables

Transmit Buffer Unavailable Enable, set together with CSR7<16> enables CSR5<2>.

Transmit Stop Enable, set together with CSR7<15> enables CSR5<1>.

Transmit Interrupt Enable, set together with CSR7<16> enables CSr5<0>.

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

ERIE

FBE

LFE

GPTE

ETIE

RWE

RSE

RUE

RIE

UNE

LPANCIE

TJE

TUE

TSE

TIE

CSR5<3>.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MX98905B | The MX98905 is designed for easy implementation of CSMA/CD local area networks, |

| MX98905B | IEEE 802.3, 10BASE5, 10BASE2 Controller and Integrated Bus Interface(IEEE 802.3, 10BASE5, 10BASE2控制器和集成總線接口) |

| MX98905BFC | The MX98905 is designed for easy implementation of CSMA/CD local area networks, |

| MXA2312A | Low Cost, +2,-2 g Dual Axis Accelerometer with Analog Outputs |

| MXA2500K | Ultra Low Cost, 【1.0 g Dual Axis Accelerometer with Absolute Outputs |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MX98726 | 制造商:MCNIX 制造商全稱:Macronix International 功能描述:SINGLE CHIP 10/100 FAST ETHERNET CONTROLLER WITH uP INTERFACE |

| MX98726AEC | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Controller Miscellaneous - Datasheet Reference |

| MX98726EC | 制造商:MCNIX 制造商全稱:Macronix International 功能描述:SINGLE CHIP 10/100 FAST ETHERNET CONTROLLER WITH uP INTERFACE |

| MX98727 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:SINGLE CHIP PCI/CARDBUS FAST ETHERNET CONTROLLER |

| MX98728 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:GMAC SINGLE CHIP 10/100 FAST ETHERNET CONTROLLER FOR GENERIC APPLICATION |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。