- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376208 > MTV412M (Electronic Theatre Controls, Inc.) PT 2C 2#20 PIN PLUG PDF資料下載

參數(shù)資料

| 型號(hào): | MTV412M |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | PT 2C 2#20 PIN PLUG |

| 中文描述: | 8051嵌入式控制器的ISP監(jiān)控128K閃存式 |

| 文件頁(yè)數(shù): | 20/26頁(yè) |

| 文件大?。?/td> | 255K |

| 代理商: | MTV412M |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)當(dāng)前第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)

MYSON-CENTURY

TECHNOLOGY

MTV412M

(Rev 0.9)

The ADC compares the input pin voltage with internal VDD*N/64 voltage (where N = 0 - 255). The ADC

output value is N when pin voltage is greater than VDD*N/255 and smaller than VDD*(N+1)/255.

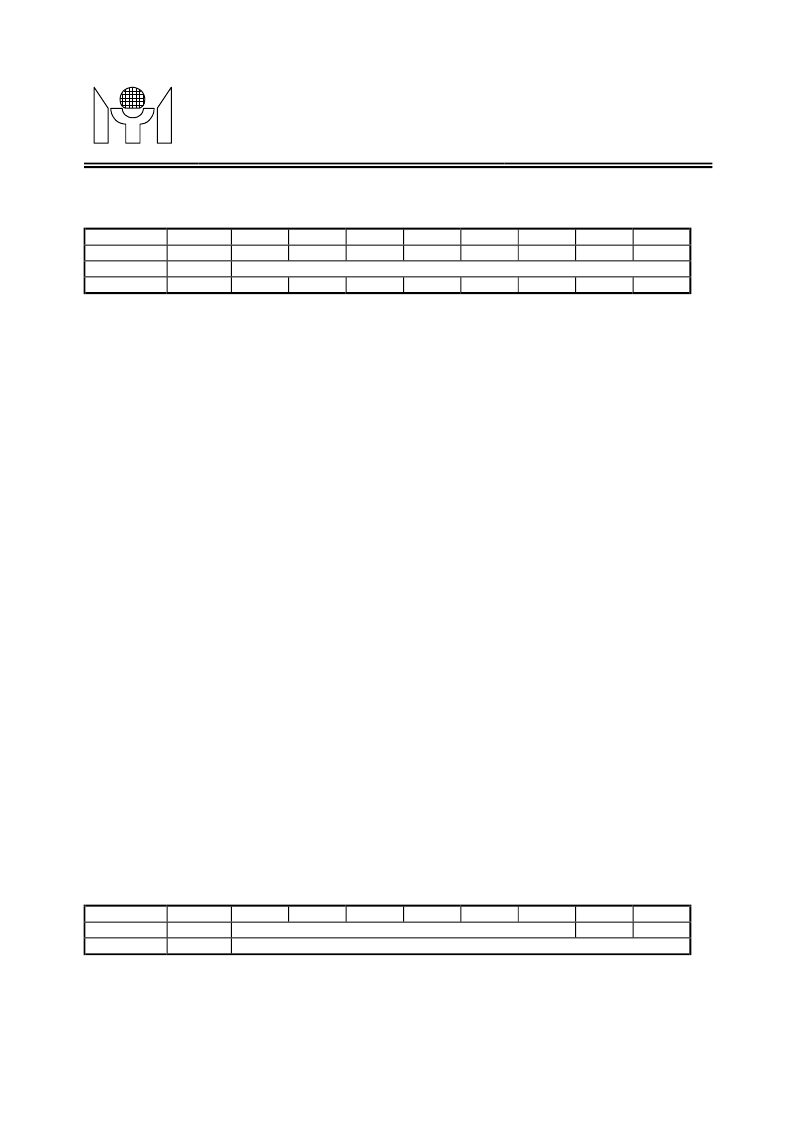

Reg name

addr

bit7

bit6

bit5

ADC

F10h (w) ENADC

ADC

F10h (r)

WDT

F18h (w)

WEN

WCLR

WDT

(w) :

Watchdog Timer control register.

WEN

= 1

→

Enables Watchdog Timer.

WCLR

= 1

→

Clears Watchdog Timer.

WDT2: WDT0 = 0

→

Overflow interval = 8 x 0.25 sec.

= 1

→

Overflow interval = 1 x 0.25 sec.

= 2

→

Overflow interval = 2 x 0.25 sec.

= 3

→

Overflow interval = 3 x 0.25 sec.

= 4

→

Overflow interval = 4 x 0.25 sec.

= 5

→

Overflow interval = 5 x 0.25 sec.

= 6

→

Overflow interval = 6 x 0.25 sec.

= 7

→

Overflow interval = 7 x 0.25 sec.

ADC

(w) :

ADC control.

ENADC

= 1

→

Enables ADC.

SADC0

= 1

→

Selects ADC0 pin input.

SADC1

= 1

→

Selects ADC1 pin input.

SADC2

= 1

→

Selects ADC2 pin input.

SADC3

= 1

→

Selects ADC3 pin input.

ADC

(r) :

ADC convert result.

11. In System Programming function (ISP)

The Flash memory can be programmed by a specific WRITER in parallel mode, or by IIC Host in serial mode

while the system is working. The features of ISP are outlined as below:

1. Single 3.3V power supply for Program/Erase/Verify.

2. Block Erase: 1024 bytes for Program Code, 10mS

3. Whole Flash erase (Blank): 10mS

4. Byte/Word programming Cycle time: 60uS per byte

5. Read access time: 50ns

6. Only one two-pin IIC bus (shared with DDC2) is needed for ISP in user/factory mode.

7. IIC Bus clock rates up to 140KHz.

8. Whole 128K-byte Flash programming within 12 Sec.

9. CRC check provides 100% coverage for all single/double bit errors.

There are two methods to enter the ISP mode which are described as below:

Method 1). The Valid ISP Slave Address and Compared data are transmitted

Method 2). Write 93h to ISP enable register (ISPEN)

Reg name

addr

bit7

bit6

bit5

ISPSLV

F0Bh(w)

ISP Slave address

ISPEN

F0Ch(w)

Write 93h to enable ISP Mode

ISPSLV

(w) :

ISP Slave IIC's address.

bit7-2 : ISP Slave IIC's address to which the ISP block should respond. The default value is 100101.

ISPEN

(w) :

Write 93h to enable ISP Mode for ISP enable method 2.

Revision 0.9 - 20 - April 2002

bit4

bit3

SADC3 SADC2 SADC1 SADC0

ADC convert result

WDT2

bit2

bit1

bit0

WDT1

WDT0

bit4

bit3

bit2

bit1

bit0

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MTV412MF128 | 8051 Embedded Monitor Controller 128K Flash Type with ISP |

| MTV412MS128 | 8051 Embedded Monitor Controller 128K Flash Type with ISP |

| MTV412MV128 | 8051 Embedded Monitor Controller 128K Flash Type with ISP |

| MU93-4001 | SUPER BRIGHT LED LIGHT BAR MODULE |

| MU04-2101 | SUPER BRIGHT LED LIGHT BAR MODULE |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MTV412MF128 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:8051 Embedded Monitor Controller 128K Flash Type with ISP |

| MTV412MS128 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:8051 Embedded Monitor Controller 128K Flash Type with ISP |

| MTV412MV128 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:8051 Embedded Monitor Controller 128K Flash Type with ISP |

| MTV-50 | 制造商:MA-COM 制造商全稱:M/A-COM Technology Solutions, Inc. 功能描述:Two-Way Power Dividers, 1 - 100 MHz and 40 - 400 MHz |

| MTV50CD35 | 制造商:Mallory Sonalert Products Inc 功能描述:Molded Case Vertical-Mount Electrolytic Radial Leads Capacitor - 50uF 35dcV -10+100% |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。