- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄359235 > MT9160AN1 (Zarlink Semiconductor Inc.) 3 Volt Multi-Featured Codec (MFC) PDF資料下載

參數(shù)資料

| 型號(hào): | MT9160AN1 |

| 廠商: | Zarlink Semiconductor Inc. |

| 元件分類: | Codec |

| 英文描述: | 3 Volt Multi-Featured Codec (MFC) |

| 中文描述: | 3伏多精選編解碼器(MFC)中 |

| 文件頁數(shù): | 1/33頁 |

| 文件大小: | 527K |

| 代理商: | MT9160AN1 |

當(dāng)前第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁

1

Zarlink Semiconductor Inc.

Zarlink, ZL and the Zarlink Semiconductor logo are trademarks of Zarlink Semiconductor Inc.

Copyright 1999-2006, Zarlink Semiconductor Inc. All Rights Reserved.

Features

Single 2.7-3.6 volt supply operation

MT91L61 version features a delayed framing

pulse in SSI and ST-BUS modes to facilitate

cascaded devices

Programmable

μ

-Law/A-Law Codec and Filters

Programmable ITU-T (G.711)/sign-magnitude

coding

Programmable transmit, receive and side-tone

gains

Fully differential interface to handset transducers

- including 300 ohm receiver driver

Flexible digital interface including ST-BUS/SSI

Serial microport

Low power operation

ITU-T G.714 compliant

Multiple power down modes

Applications

Battery operated equipment

Digital telephone sets

Cellular radio sets

Local area communications stations

Pair Gain Systems

Line cards

March 2006

Ordering Information

MT91L61AE

MT91L60AE

MT91L61AS

MT91L60AS

MT91L61AN

MT91L60AN

MT91L60ASR

MT91L61ASR

MT91L61ASR1

MT9160AN1

24 Pin PDIP

24 Pin PDIP

24 Pin SOIC

20 Pin SOIC

24 Pin SSOP

20 Pin SSOP

20 Pin SOIC

24 Pin SOIC

24 Pin SOIC*

20 Pin SSOP*

*Pb Free Matte Tin

Tubes

Tubes

Tubes

Tubes

Tubes

Tubes

Tape & Reel

Tape & Reel

Tape & Reel

Tubes

-40

°

C to +85

°

C

ISO

2

-CMOS

MT91L60/61

3 Volt Multi-Featured Codec (MFC)

Data Sheet

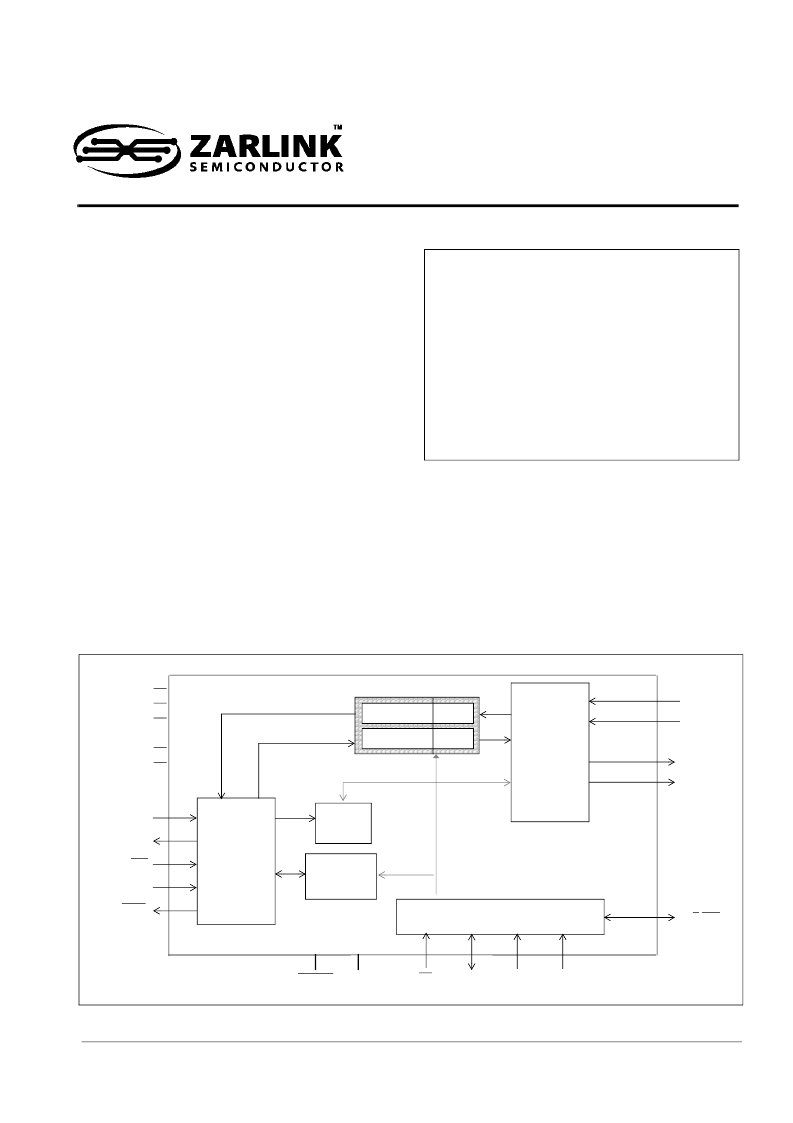

Figure 1 - Functional Block Diagram

M -

M +

HSPKR +

HSPKR -

FILTER/CODEC GAIN

ENCODER

DECODER

7dB

-7dB

Transducer

Interface

Flexible

Digital

Interface

Timing

ST-BUS

C & D

Channels

Serial Microport

A/

μ

/IRQ

VSSD

VDD

VSSA

VBias

VRef

Din

Dout

STB/F0i

CLOCKin

PWRST

IC

CS

DATA1

DATA2

SCLK

STBd/FOod

(MT91L61only)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MT91610 | Programmable Ringing SLIC |

| MT91610AQ | Programmable Ringing SLIC |

| MT91610 | Analog Ringing SLIC |

| MT91610AQ | Analog Ringing SLIC |

| MT9162AN1 | 5 Volt Single Rail Codec |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MT9160AS | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| MT9160B | 制造商:MITEL 制造商全稱:Mitel Networks Corporation 功能描述:ISO2-CMOS 5 Volt Multi-Featured Codec (MFC) |

| MT9160BE | 制造商:Microsemi Corporation 功能描述:MULTI-FEATURED CODEC 24PDIP - Rail/Tube |

| MT9160BN | 制造商:Microsemi Corporation 功能描述: |

| MT9160BS | 制造商:Microsemi Corporation 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。