- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383645 > MT90810 (Mitel Networks Corporation) Flexible MVIP(Multi-Vendor Integration Protocol) Interface Circuit(彈性MVIP接口電路) PDF資料下載

參數(shù)資料

| 型號: | MT90810 |

| 廠商: | Mitel Networks Corporation |

| 英文描述: | Flexible MVIP(Multi-Vendor Integration Protocol) Interface Circuit(彈性MVIP接口電路) |

| 中文描述: | 柔性MVIP(多廠商集成協(xié)議)接口電路(彈性MVIP接口電路) |

| 文件頁數(shù): | 22/33頁 |

| 文件大?。?/td> | 176K |

| 代理商: | MT90810 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁當前第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁

MT90810

Preliminary Information

2-190

registers are described in a subsequent

section. The received input data is sampled at

the rising edge of the TCK pulses. When TDI is

not driven from an external source, the test

logic perceives a logic 1.

The Test Data Output (TDO)

Depending on the sequence previously applied

to the TMS input, the contents of either the

instruction register or a data register are

serially shifted out towards the TDO. The data

out of the TDO is clocked at the falling edge of

the TCK pulses. When no data is shifted

through the cells, the TDO driver is set to an

inactive state.

Instruction Register

In accordance with the IEEE 1149.1 standard, the

FMIC uses public instructions listed in Table 23 -

“Instruction Register” . The FMIC JTAG Interface

contains a two bit instruction register. Instructions

are serially loaded into the Instruction Register from

the TDI when the TAP Controller is in its Shift-IR

state. Subsequently, the instructions are decoded to

achieve two basic functions: to select the test data

register that may operate while the instruction is

current and to define the serial test data register path

that is used to shift data between TDI and TDO

during data register scanning.

Test Data Registers

As specified in the IEEE 1149.1 Standard, the FMIC

JTAG interface contains two test data registers:

The Boundary Scan Register

The Boundary-Scan Register consists of a

series of Boundary-Scan Cells arranged to form

a scan path around the boundary of the core

logic of the FMIC.

The Bypass Register

The Bypass Register is a single stage

shift-register that provides a one-bit path that

minimizes the distance for test data shifting

from the FMIC’s TDI to its TDO.

The FMIC boundary-scan register contains 84 bits.

Bit 0 in Table 24 - “Boundary Scan Register” is the

first bit clocked out. All tristate enable bits are

asserted high i.e., a logic 1 enables the

corresponding group of outputs/bidirectionals. Note

that clocking all zeros into the scan path register will

set all outputs to tristate.

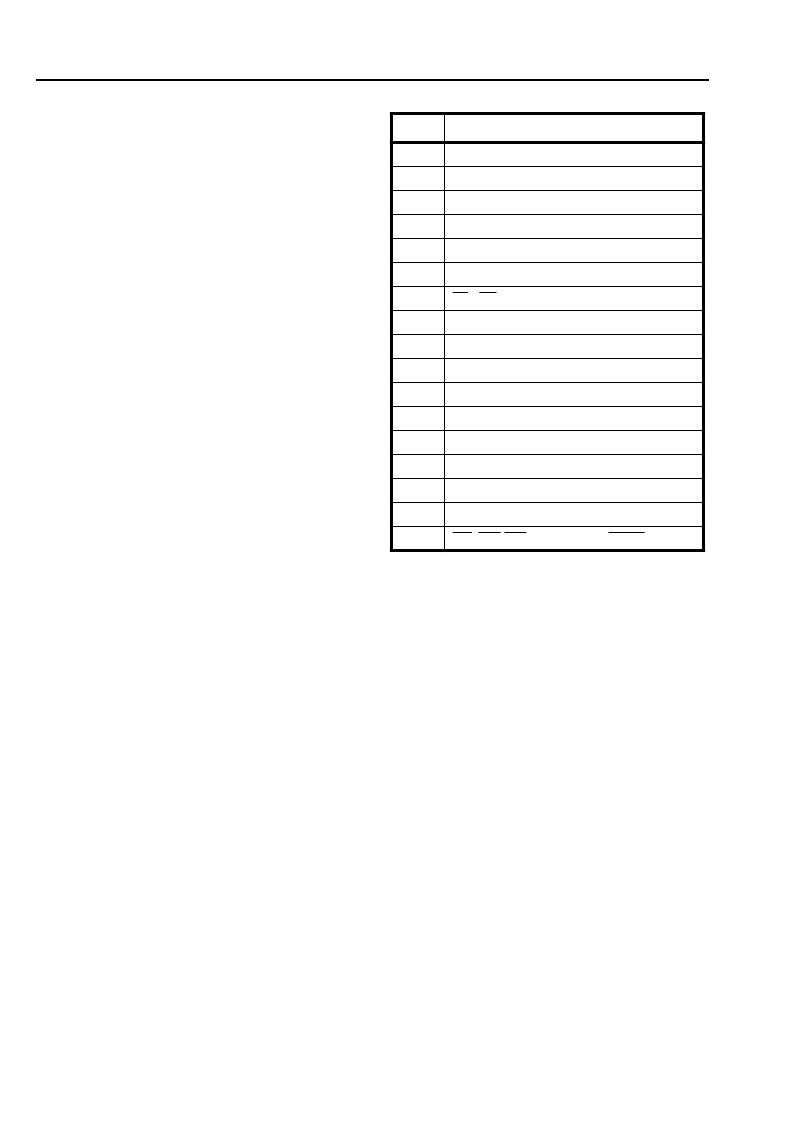

Bits

Definition

0:11

FGB[11:0]

12:23

FGA[11:0]

24:31

DSo[7:0]

32

tristate enable for DSo[7:0]

33:40

DSi[7:0]

41

tristate enable for DSi[7:0]

42:45

F0 , C4 , C2 , SEC8K

46

tristate enable for

47:51

FRAME, CLK8, CLK4, CLK2, CSTo

52

tristate enable for ALL output only pins

53:54

EX8KA, EX8KB

55:58

LDO[3:0]

59:62

LDI[3:0]

63:70

D[7:0]

71

tristate enable for D[7:0]

72:75

RDY, ERR, DREQ[1:0]

76:83

RD, WR, CS, ALE, A[1:0], DACK[1:0]

Table 24

-

Boundary Scan Register

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MT90812 | Integrated Digital Switch (IDX)(集成數(shù)字開關(guān)) |

| MT90840AK | Distributed Hyperchannel Switch |

| MT90840AP | Distributed Hyperchannel Switch |

| MT9085B | PAC - Parallel Access Circuit(并行存取電路) |

| MT9092 | Digital Telephone with HDLC(數(shù)字電話(帶高階數(shù)據(jù)鏈路控制HDLC)) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MT90810AK | 制造商:Microsemi Corporation 功能描述: |

| MT90812 | 制造商:MITEL 制造商全稱:Mitel Networks Corporation 功能描述:Integrated Digital Switch (IDX) |

| MT90812AL | 制造商:Microsemi Corporation 功能描述:SWIT FABRIC 192 X 192 16.384MBPS 5V 64MQFP - Trays 制造商:Zarlink Semiconductor Inc 功能描述:SWIT FABRIC 192 X 192 16.384MBPS 5V 64MQFP - Trays |

| MT90812AL1 | 制造商:Microsemi Corporation 功能描述:SWIT FABRIC 192 X 192 16.384MBPS 5V 64MQFP - Trays 制造商:Microsemi Corporation 功能描述:PB FREE INTEGRATED DIGITAL SWITCH |

| MT90812AP | 制造商:MITEL 制造商全稱:Mitel Networks Corporation 功能描述:Integrated Digital Switch (IDX) |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。