- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄45390 > MSM6542-03GS-VK (OKI ELECTRIC INDUSTRY CO LTD) 0 TIMER(S), REAL TIME CLOCK, PDSO24 PDF資料下載

參數(shù)資料

| 型號(hào): | MSM6542-03GS-VK |

| 廠商: | OKI ELECTRIC INDUSTRY CO LTD |

| 元件分類: | 時(shí)鐘/數(shù)據(jù)恢復(fù)及定時(shí)提取 |

| 英文描述: | 0 TIMER(S), REAL TIME CLOCK, PDSO24 |

| 封裝: | 0.430 INCH, PLASTIC, SOP-24 |

| 文件頁(yè)數(shù): | 21/54頁(yè) |

| 文件大?。?/td> | 406K |

| 代理商: | MSM6542-03GS-VK |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)當(dāng)前第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)

Semiconductor

MSM6542-01/02/03

95

When an IRQ FLAG bits are read mistakenly due to external noise, particularly

erroneous read signal noise which is generated when the standby power supply

voltage is switched to the system power supply voltage or vice versa, therefore, the

IRQ FLAG bits are not cleared immediately but read at the correct times.

When 1 is written in the DP bit, the bit is immediately set at 1 except the following two

cases.

(i)

The CS

1 bit is low.

(ii)

For 62

s immediately after the DP bit changes from 1 to 0.

Writing 0 in the DP bit, that is, canceling data protection is allowed only when:

(i)

Zero is written in the DP bit more than 2 ms after CS

1 changes from low to high.

(ii)

The CS

1 bit is high 11 ms after 0 is written in the DP bit.

b) CAL (D

1) (CALendar)

This bit specifies a range in which the realtime counter is incremented. When the bit is 1,

the R-S

1 to R-Y10 and R-W register can be incremented. When the bit is 0, the R-S1 to R-H10

and R-W registers can be incremented.

With the CAL bit set at 1, R-D

1 to R-Y10 are used as realtime registers. Therefore, setting an

impossible time in these registers causes an error. For the bits marked an asterisk (*) of the

R-D

10 and R-MO10 registers in the register table, when 1 is written, 0 is automatically set. The

alarm comparison range is specified by the A-ENABLE register.

When the CAL bit is 0, the R-D

1 to R-Y10 registers are not incremented. They can be used as

static RAM, enabling arbitrary values to be set. The bits marked an asterisk (*) of the R-D

10

and R-MO

10 registers in the register table can be subject to both write and read operations.

The alarm comparison range is specified by the A-ENABLE register. However, the R-D

1 to

R-Y

10 registers are assumed to always provide a match. When these registers are used as

static RAM, they cannot be rewritten when the DP bit is 1.

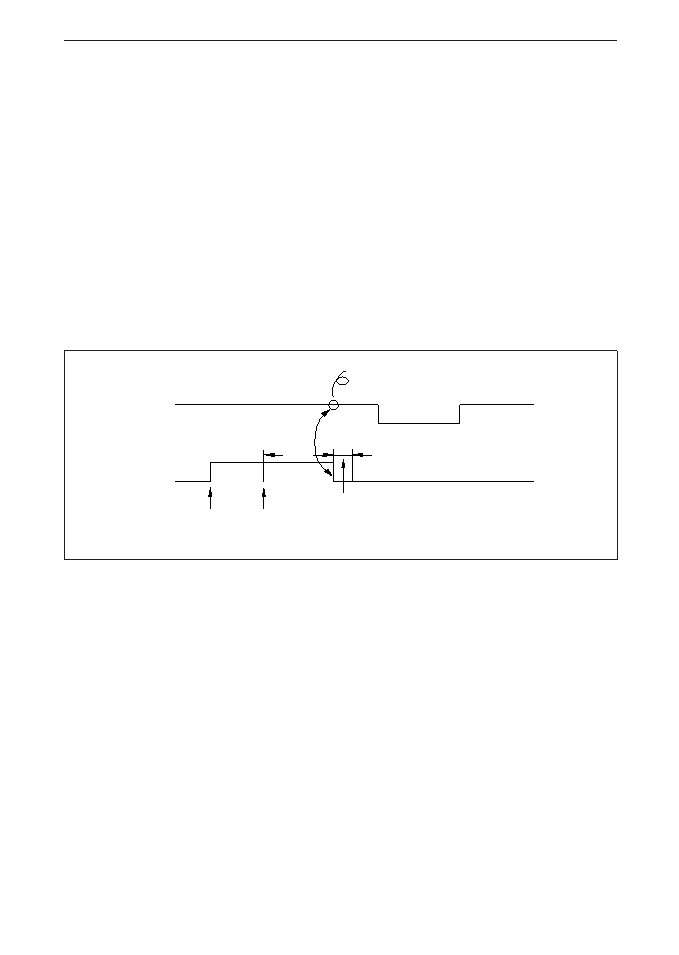

CS1

Data protection can be canceled

because CS1 is high

0 is written

in the DPbit

DPbit

1 is written

in the DPbit

11ms

1 written in the DPbit

in this period is ignored

62s

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MSM6542-03RS | 0 TIMER(S), REAL TIME CLOCK, PDIP24 |

| MSM65513-GS-VK | 8-BIT, MROM, 12 MHz, MICROCONTROLLER, PQFP64 |

| MSM65513-JS | 8-BIT, MROM, 12 MHz, MICROCONTROLLER, PQCC68 |

| MSM65513-XXSS | 8-BIT, MROM, 10 MHz, MICROCONTROLLER, PDIP64 |

| MSM65513GS | 8-BIT, MROM, 10 MHz, MICROCONTROLLER, PQFP64 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MSM6544 | 制造商:OKI 制造商全稱:OKI electronic componets 功能描述:42-DOT LCD DRIVER |

| MSM6544GS-2KR1 | 制造商:ROHM Semiconductor 功能描述: |

| MSM6545 | 制造商:OKI 制造商全稱:OKI electronic componets 功能描述:Operatable at 0.9 V and Built-in Buzzer Circuit 4-Bit Microcontroller |

| MSM6545L | 制造商:OKI 制造商全稱:OKI electronic componets 功能描述:Operatable at 0.9 V and Built-in Buzzer Circuit 4-Bit Microcontroller |

| MSM6545L-XXGS-2K | 制造商:OKI 制造商全稱:OKI electronic componets 功能描述:Operatable at 0.9 V and Built-in Buzzer Circuit 4-Bit Microcontroller |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。