- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄45388 > MSC8144VT800B (FREESCALE SEMICONDUCTOR INC) 133 MHz, OTHER DSP, PBGA783 PDF資料下載

參數(shù)資料

| 型號: | MSC8144VT800B |

| 廠商: | FREESCALE SEMICONDUCTOR INC |

| 元件分類: | 數(shù)字信號處理 |

| 英文描述: | 133 MHz, OTHER DSP, PBGA783 |

| 封裝: | 29 X 29 MM, LEAD FREE, PLASTIC, FCPBGA-783 |

| 文件頁數(shù): | 44/80頁 |

| 文件大?。?/td> | 1250K |

| 代理商: | MSC8144VT800B |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁當(dāng)前第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁

Electrical Characteristics

MSC8144 Quad Core Digital Signal Processor Data Sheet, Rev. 16

Freescale Semiconductor

49

2.6.5.6

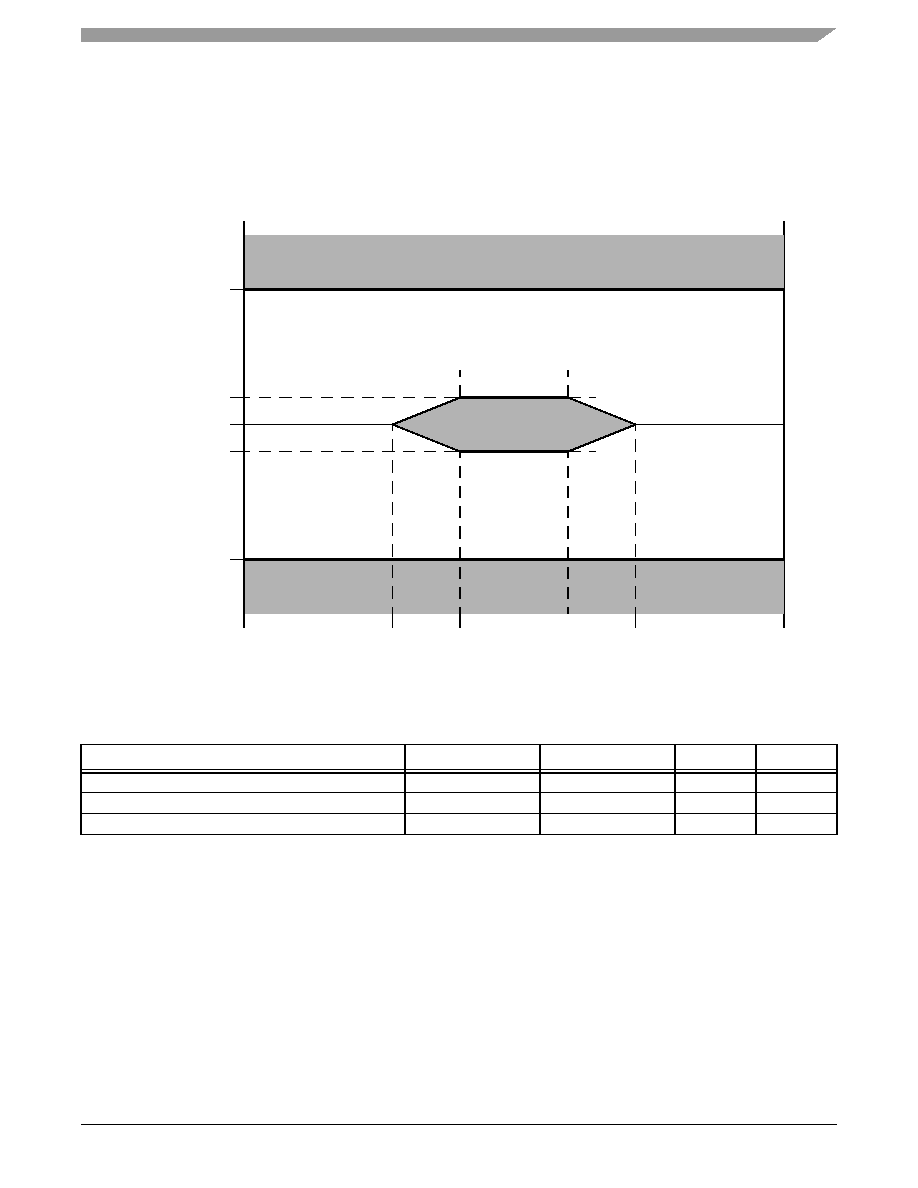

Receiver Eye Diagrams

For each baud rate at which an LP-Serial receiver is specified to operate, the receiver shall meet the corresponding bit error rate

specification (Table 32, Table 33, and Table 34) when the eye pattern of the receiver test signal (exclusive of sinusoidal jitter)

falls entirely within the unshaded portion of the receiver input compliance mask shown in Figure 14 with the parameters

specified in Table 35. The eye pattern of the receiver test signal is measured at the input pins of the receiving device with the

device replaced with a 100

Ω ±5% differential resistive load.

2.6.5.7

Measurement and Test Requirements

Since the LP-Serial electrical specification are guided by the XAUI electrical interface specified in Clause 47 of IEEE Std.

802.3ae-2002, the measurement and test requirements defined here are similarly guided by Clause 47. In addition, the CJPAT

test pattern defined in Annex 48A of IEEE Std. 802.3ae-2002 is specified as the test pattern for use in eye pattern and jitter

measurements. Annex 48B of IEEE Std. 802.3ae-2002 is recommended as a reference for additional information on jitter test

methods.

Figure 14. Receiver Input Compliance Mask

Table 35. Receiver Input Compliance Mask Parameters Exclusive of Sinusoidal Jitter

Receiver Type

VDIFFmin (mV)

VDIFFmax (mV)

A (UI)

B (UI)

1.25 GBaud

100

800

0.275

0.400

2.5 GBaud

100

800

0.275

0.400

3.125 GBaud

100

800

0.275

0.400

1

0

VDIFF max

–VDIFF max

VDIFF min

–VDIFF min

Time (UI)

R

e

ce

iv

er

D

if

fe

rent

ial

Inp

u

tV

o

lt

age

0

A

B

1 – B

1 – A

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MSC8144SVT1000A | 133 MHz, OTHER DSP, PBGA783 |

| MSC8144TVT1000A | 133 MHz, OTHER DSP, PBGA783 |

| MSC8144SVT1000B | 133 MHz, OTHER DSP, PBGA783 |

| MSC8144VT1000A | 133 MHz, OTHER DSP, PBGA783 |

| MSC8144SVT800A | 133 MHz, OTHER DSP, PBGA783 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MSC81450M | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:RF & MICROWAVE TRANSISTORS AVIONICS APPLICATIONS |

| MSC8151 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:Single-Core Digital Signal Processor |

| MSC8151SAG1000B | 制造商:Freescale Semiconductor 功能描述:STARCORE DSP, 1X 1GHZ SC3850 CORES, MAPLE-B ACCELERATOR, DDR - Bulk 制造商:Freescale Semiconductor 功能描述:STARCORE DSP, 1X 1GHZ SC3850 CORES, MAPLE-B ACCELERATOR, DDR - Trays 制造商:Freescale Semiconductor 功能描述:IC DSP 1X 1GHZ SC3850 783FCBGA |

| MSC8151SVT1000B | 功能描述:數(shù)字信號處理器和控制器 - DSP, DSC Darwin RoHS:否 制造商:Microchip Technology 核心:dsPIC 數(shù)據(jù)總線寬度:16 bit 程序存儲器大小:16 KB 數(shù)據(jù) RAM 大小:2 KB 最大時鐘頻率:40 MHz 可編程輸入/輸出端數(shù)量:35 定時器數(shù)量:3 設(shè)備每秒兆指令數(shù):50 MIPs 工作電源電壓:3.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TQFP-44 安裝風(fēng)格:SMD/SMT |

| MSC8151TVT1000B | 功能描述:數(shù)字信號處理器和控制器 - DSP, DSC Darwin RoHS:否 制造商:Microchip Technology 核心:dsPIC 數(shù)據(jù)總線寬度:16 bit 程序存儲器大小:16 KB 數(shù)據(jù) RAM 大小:2 KB 最大時鐘頻率:40 MHz 可編程輸入/輸出端數(shù)量:35 定時器數(shù)量:3 設(shè)備每秒兆指令數(shù):50 MIPs 工作電源電壓:3.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TQFP-44 安裝風(fēng)格:SMD/SMT |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。