- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371014 > MC145202-1 (Motorola, Inc.) PLL Frequency Synthesizer(2.0GHz PLL頻率合成器) PDF資料下載

參數(shù)資料

| 型號: | MC145202-1 |

| 廠商: | Motorola, Inc. |

| 英文描述: | PLL Frequency Synthesizer(2.0GHz PLL頻率合成器) |

| 中文描述: | 鎖相環(huán)頻率合成器(2.0GHz的鎖相環(huán)頻率合成器) |

| 文件頁數(shù): | 1/23頁 |

| 文件大小: | 270K |

| 代理商: | MC145202-1 |

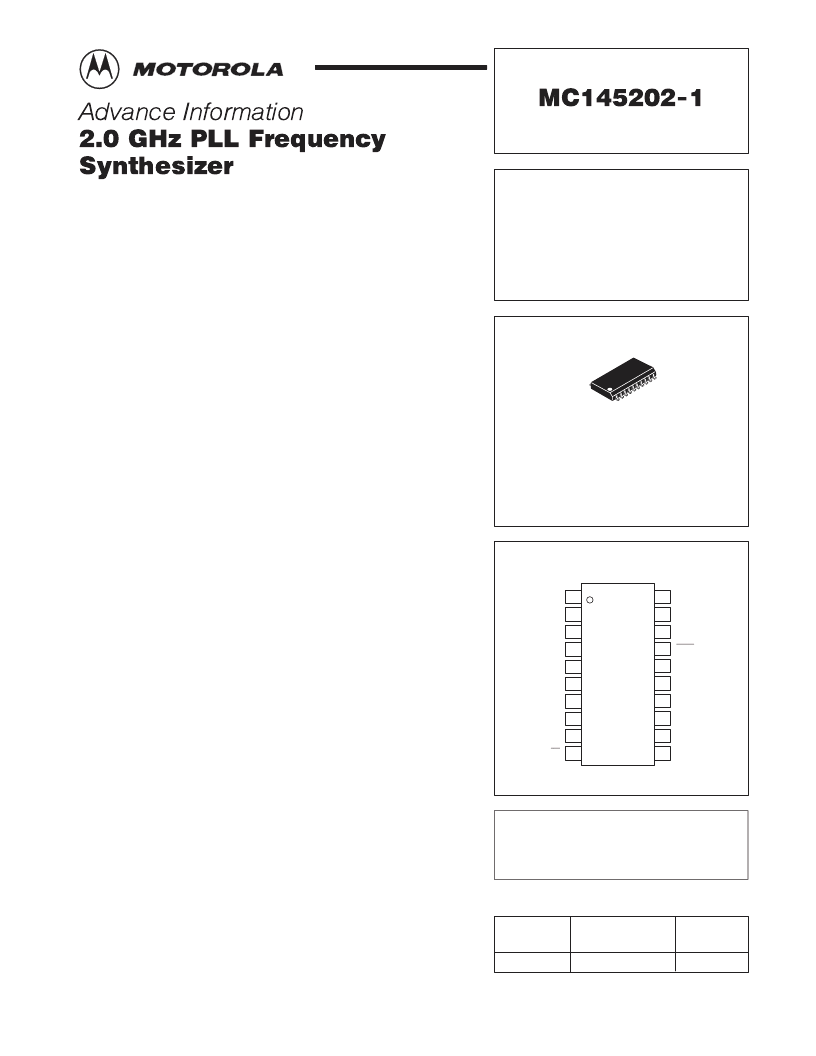

Device

Operating

Temperature Range

Package

SEMICONDUCTOR

TECHNICAL DATA

PLL FREQUENCY

SYNTHESIZER

ORDERING INFORMATION

MC145202F1

TA = –40 to 85

°

C

SO–20

F SUFFIX

PLASTIC PACKAGE

CASE 751J

(SO–20)

20

1

PIN CONNECTIONS

Order this document by MC145202–1/D

1

2

3

4

5

6

7

8

9

10

20

19

18

17

16

15

14

13

(Top View)

REFout

LD

φ

R

φ

V

REFin

Din

CLK

ENB

Output A

Output B

VDD

Test 2

12

11

Test 1

VCC

fin

VPD

PDout

Gnd

Rx

fin

EVALUATION KIT

The P/N MC145202–1EVK, which contains

hardware and software, is available.

1

SOLUTIONS – RF AND IF DEVICE DATA

The MC145202–1 is pin–for–pin compatible with the previous generation

MC145200, MC145201, and MC145202. Table 1 highlights the differences in

the four devices. The MC145202–1 is recommended for new designs and

has improved suppression of reference sideband spurs.

The counters are programmed via a synchronous serial port which is SPI

compatible. The serial port is byte-oriented to facilitate control via an MCU.

Due to the innovative BitGrabber Plus

registers, the MC145202–1 may be

cascaded with other peripherals featuring BitGrabber Plus without requiring

leading dummy bits or address bits in the serial data stream. In addition,

BitGrabber Plus peripherals may be cascaded with existing BitGrabber

peripherals.

The device features a single–ended current source/sink phase detector A

output and a double–ended phase detector B output. Both phase detectors

have linear transfer functions (no dead zones). The maximum current of the

single–ended phase detector output is determined by an external resistor

tied from the Rx pin to ground. This current can be varied via the serial port.

Slew–rate control is provided by a special driver designed for the REFout

pin. This minimizes interference caused by REFout.

This part includes a differential RF input that may be operated in a

single–ended mode. Also featured are on–board support of an external

crystal and a programmable reference output. The R, A, and N counters are

fully programmable. The C register (configuration register) allows the part to

be configured to meet various applications. A patented feature allows the C

register to shut off unused outputs, thereby minimizing system noise and

interference.

In order to have consistent lock times and prevent erroneous data from

being loaded into the counters, on–board circuitry synchronizes the update

of the A register if the A or N counters are loading. Similarly, an update of the

R register is synchronized if the R counter is loading.

The double–buffered R register allows new divide ratios to be presented

to the three counters (R, A, and N) simultaneously.

Maximum Operating Frequency: 2000 MHz @ – 10 dBm

Operating Supply Current: 4 mA Nominal at 3.0 V

Operating Supply Voltage Range (VDD, VCC, VPD Pins): 2.7 to 5.5 V

Current Source/Sink Phase Detector Output:

1.7 mA @ 5.0 V or 1.0 mA @ 3.0 V

Gain of Current Source/Sink Phase/Frequency Detector Controllable via

Serial Port

R Counter Division Range: 1 and 5 to 8191

Dual–Modulus Capability Provides Total Division up to 262,143

High–Speed Serial Interface: 4 Mbps

Output A Pin, When Configured as Data Out, Permits Cascading of

Devices

Two General–Purpose Digital Outputs:

Output A: Totem–Pole (Push–Pull) with Four Output Modes

Output B: Open–Drain

Patented Power–Saving Standby Feature with Orderly Recovery for

Minimizing Lock Times, Standby Current: 30

μ

A

See App Note AN1253/D for Low–Pass Filter Design, and AN1277/D for

Offset Reference PLLs for Fine Resolution or Fast Hopping

BitGrabber and BitGrabber Plus are trademarks of Motorola, Inc.

This document contains information on a new product. Specifications and information herein

are subject to change without notice.

Motorola, Inc. 2000

Rev 0

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MC145225 | Dual PLL Frequency Synthesizers With DACs and Voltage Multipliers(帶DACs和電壓乘法器的雙PLL頻率合成器) |

| MC145230 | Dual PLL Frequency Synthesizers With DACs and Voltage Multipliers(帶DACs和電壓乘法器的雙PLL頻率合成器) |

| MC14528BCL | Dual Monostable Multivibrator |

| MC14528 | DEFLECTION PROCESSOR FOR MULTISYNC MONITORS |

| MC14528 | Dual Monostable Multivibrator |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MC14520B | 制造商:Motorola Inc 功能描述: 制造商:ON Semiconductor 功能描述: |

| MC14520BAL | 制造商:Motorola Inc 功能描述:Counter, Up, 4 Bit Binary, 16 Pin, Ceramic, DIP |

| MC14520BCP | 功能描述:計數(shù)器移位寄存器 3-18V Dual BCD Up RoHS:否 制造商:Texas Instruments 計數(shù)器類型: 計數(shù)順序:Serial to Serial/Parallel 電路數(shù)量:1 封裝 / 箱體:SOIC-20 Wide 邏輯系列: 邏輯類型: 輸入線路數(shù)量:1 輸出類型:Open Drain 傳播延遲時間:650 ns 最大工作溫度:+ 125 C 最小工作溫度:- 40 C 封裝:Reel |

| MC14520BCPG | 功能描述:計數(shù)器移位寄存器 3-18V Dual BCD Up RoHS:否 制造商:Texas Instruments 計數(shù)器類型: 計數(shù)順序:Serial to Serial/Parallel 電路數(shù)量:1 封裝 / 箱體:SOIC-20 Wide 邏輯系列: 邏輯類型: 輸入線路數(shù)量:1 輸出類型:Open Drain 傳播延遲時間:650 ns 最大工作溫度:+ 125 C 最小工作溫度:- 40 C 封裝:Reel |

| MC14520BDW | 功能描述:計數(shù)器移位寄存器 3-18V Dual BCD Up RoHS:否 制造商:Texas Instruments 計數(shù)器類型: 計數(shù)順序:Serial to Serial/Parallel 電路數(shù)量:1 封裝 / 箱體:SOIC-20 Wide 邏輯系列: 邏輯類型: 輸入線路數(shù)量:1 輸出類型:Open Drain 傳播延遲時間:650 ns 最大工作溫度:+ 125 C 最小工作溫度:- 40 C 封裝:Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。