- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377895 > MB86960APF-G (Fujitsu Limited) NETWORK INTERFACE CONTROLLER with ENCODER/DECODER (NICE) PDF資料下載

參數(shù)資料

| 型號: | MB86960APF-G |

| 廠商: | Fujitsu Limited |

| 英文描述: | NETWORK INTERFACE CONTROLLER with ENCODER/DECODER (NICE) |

| 中文描述: | 網(wǎng)絡(luò)接口控制器的編碼/解碼器(尼斯) |

| 文件頁數(shù): | 10/65頁 |

| 文件大小: | 488K |

| 代理商: | MB86960APF-G |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁當(dāng)前第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁

MB86960

CONTROLLER

ENCODER/

DECODER

NICE

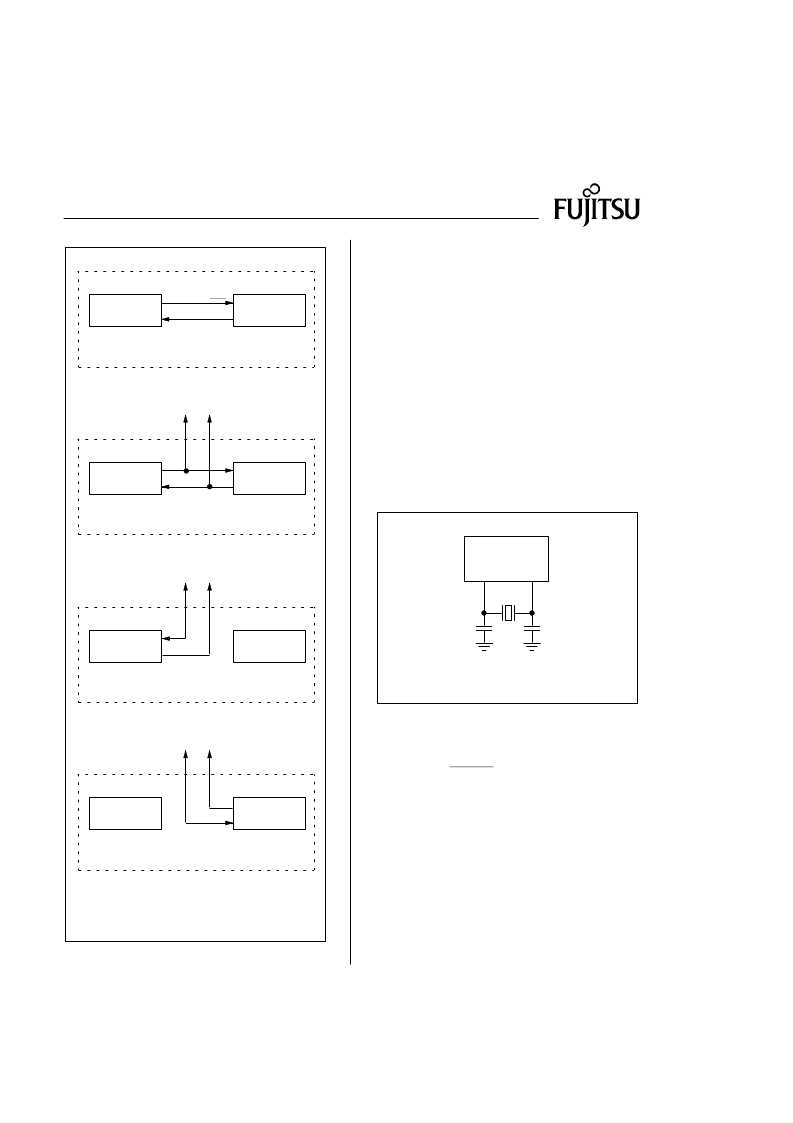

CASE 00: NORMAL NICE MODE

CONTROLLER

ENCODER/

DECODER

NICE

CASE 01: NICE + MONITOR

CONTROLLER

ENCODER/

DECODER

NICE

CASE 10: ENCODER/DECODER BYPASS

CONTROLLER

ENCODER/

DECODER

NICE

CASE 01: NICE + MONITOR

CONTROLLER TEST

EED TEST

RXD, RXC

CRS, TCK, COL

TEN, TXD, LBC

Figure 2. Encoder/Decoder Modes

CRYSTAL OSCILLATOR

The ISO/ANSI/IEEE 8802–3 international LAN stan-

dard specifies a bit clock rate of 10 Mbit/sec. This is

obtained from a 20 MHz clock generated by the on-chip

oscillator, which operates from an external crystal

connected between pins X1 and X2 on the NICE chip.

Crystal capacitance as specified by the manufacturer

should be connected from X1 and X2 to ground,

considering any stray capacitance which can vary the

crystal’s frequency. See Figure 3 for typical values. A

crystal with the following specifications is recom-

mended: quartz (AT-cut; 20 MHz; frequency/accuracy of

±

50

ppm at 25 C to 70 C; parallel resonant with 20 pF

load in a fundamental mode. Possible vendors include:

Ecliptek

Corp.

(Costa

ECSM200-20.000; and M-tron Industries, Inc. (Yank-

ton, SD), p/n MP-1 & MP-2, with 20MHz, 50ppm over

0 C to 70 C, and 18 pF fundamental load.

Mesa,

CA),

p/n

NICE

X1

X2

20 MHz

18 pF

18 pF

Figure 3. Crystal Connection

The clock also serves as a reference for an internal phase

locked loop which is used for clock recovery in the

decoder section. Internal clocks are shut down when

DLCR7 bit 5, PWRDN, is invoked for Power Down

Mode.

SRAM CONFIGURATIONS

Eight different configurations of SRAM for the packet

buffer are possible as illustrated in Figure 4. First, the

width of the SRAM data path can be 8 or 16 bits, selected

by programming the Buffer Byte/Buffer Word (BB/BW)

bit, bit 4 of DLCR6. If this bit is set to 1, byte-wide data is

selected; if set to 0, the width is word-wide (16 bits). The

SB/SW Bit, DLCR6 bit 5, selects the system bus width,

while the BB/BW Bit, DLCR6 bit 4 selects the SRAM

buffer width. Secondly, the depth of the SRAM is

programmed by setting Buffer Size 1 and 0 (BS1 and

BS0), bits 1 and 0 in DLCR6. Depth selections are 8, 16,

32 or 64 kilobytes.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MB86961A | UNIVERSAL INTERFACE FOR 10BASET |

| MB86961APD-G | UNIVERSAL INTERFACE FOR 10BASET |

| MB86961APF-G | UNIVERSAL INTERFACE FOR 10BASET |

| MB86965 | EtherCoupler ETHERNET CONTROLLER WITH 10BASE?T TRANSCEIVER |

| MB86965B | EtherCoupler ETHERNET CONTROLLER WITH 10BASE?T TRANSCEIVER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MB86961A | 制造商:FUJITSU 制造商全稱:Fujitsu Component Limited. 功能描述:UNIVERSAL INTERFACE FOR 10BASET |

| MB86961APD-G | 制造商:FUJITSU 制造商全稱:Fujitsu Component Limited. 功能描述:UNIVERSAL INTERFACE FOR 10BASET |

| MB86961APF-G | 制造商:FUJITSU 制造商全稱:Fujitsu Component Limited. 功能描述:UNIVERSAL INTERFACE FOR 10BASET |

| MB86965 | 制造商:FUJITSU 制造商全稱:Fujitsu Component Limited. 功能描述:EtherCoupler ETHERNET CONTROLLER WITH 10BASE?T TRANSCEIVER |

| MB86965B | 制造商:FUJITSU 制造商全稱:Fujitsu Component Limited. 功能描述:EtherCoupler ETHERNET CONTROLLER WITH 10BASE?T TRANSCEIVER |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。