- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370973 > M5M4V16169DRT-8 (Mitsubishi Electric Corporation) 22182053 PDF資料下載

參數(shù)資料

| 型號: | M5M4V16169DRT-8 |

| 廠商: | Mitsubishi Electric Corporation |

| 英文描述: | 22182053 |

| 中文描述: | 16MCDRAM:16米(100萬字由16位)與16K的緩存內(nèi)存(1024字由16位)的SRAM |

| 文件頁數(shù): | 16/64頁 |

| 文件大小: | 737K |

| 代理商: | M5M4V16169DRT-8 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁當前第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁

M5M4V16169DTP/RT-7,-8,-10,-15

16MCDRAM:16M(1M-WORD BY 16-BIT) CACHED DRAM WITH 16K (1024-WORD BY 16-BIT) SRAM

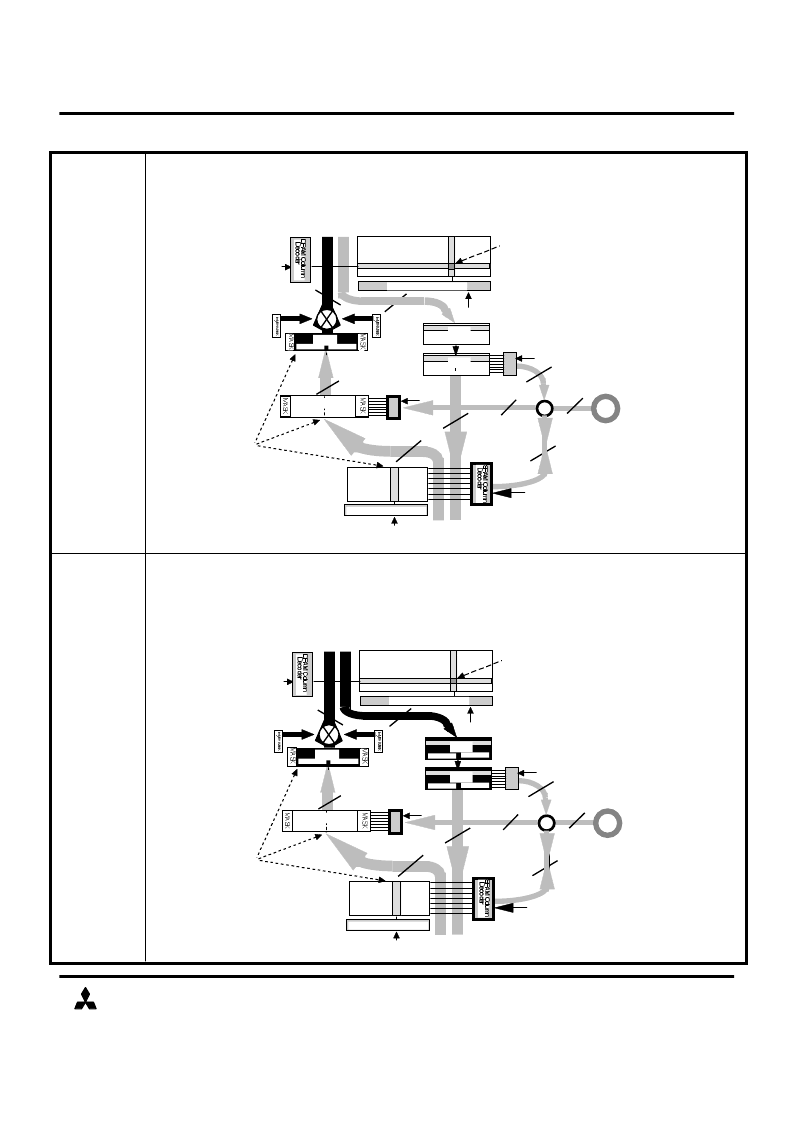

MODE DESCRIPTIONS (9)

MITSUBISHI LSIs

(REV 1.0) Jul. 1998

MITSUBISHI ELECTRIC

DRAM Write

Transfer4

DRAM Write

Transfer4

& Read

Data (8X16 Block) is transferred from WB2 to the DRAM block specified by Addresses Ad3-

Ad7. Addresses Ad8-Ad9 must be set to Low. The Mask present in Byte MaskRegister

controls the data written to the DRAM. With the DWT4 function, the WB2 data and WB2 Mask

remain unchanged. (Note 4,5)

Data (8X16 Block) is transferred from WB2 to the DRAM block specified by Addresses Ad3-

Ad7. Addresses Ad8-Ad9 must be set to Low. The Mask present in Byte MaskRegister

controls the data written to the DRAM. With the DWT4R function, the WB2 data and WB2

transfer mask remain unchanged. The block to which the data is written in DRAM is

simultaneously transferred to the Read Buffer. (Notes 1,2,4,5)

16

X

DQs

SRAM

1KX16

8X16

8X16

8X16

8X16

8X16

16bits

16bits

16bits

As3-9

1of128Decode

SRAM RowDecoder

DRAM

256KX16

Ad0-11

1of4096Decode

Ad3-7

1of32

Decode

As0-2

1of8

Decode

As0-2

1of8Decode

8X16Block

8X16Block

WB1

Upper Byte

Lower Byte

Upper Byte

Lower Byte

DRAM RowDecoder

16bits

As0-2

1of8Decode

Lower Byte

RB2

Lower Byte

RB1

DQs

SRAM

1KX16

8X16

8X16

8X16

8X16

8X16

16bits

16bits

As3-9

1of128Decode

SRAM RowDecoder

DRAM

256KX16

Ad0-11

1of4096Decode

Ad3-7

1of32

Decode

As0-2

1of8

Decode

As0-2

1of8Decode

8X16Block

8X16Block

Upper Byte

Lower Byte

Upper Byte

Lower Byte

DRAM RowDecoder

16bits

As0-2

1of8Decode

Lower Byte

RB2

Lower Byte

RB1

WB1

X

16bits

DQ8-15

DQ0-7

DQ8-15

DQ0-7

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M5M4V16G50DFP-10 | 16M (2-BANK x 262144-WORD x 32-BIT) Synchronous Graphics RAM |

| M5M4V16G50DFP-12 | 16M (2-BANK x 262144-WORD x 32-BIT) Synchronous Graphics RAM |

| M5M4V16G50DFP-8 | 16M (2-BANK x 262144-WORD x 32-BIT) Synchronous Graphics RAM |

| M5M4V64S20ATP-10 | 64M (4-BANK x 4194304-WORD x 4-BIT) Synchronous DRAM |

| M5M4V64S20ATP-10L | 64M (4-BANK x 4194304-WORD x 4-BIT) Synchronous DRAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M5M4V16169DTP | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:16MCDRAM:16M(1M-WORD BY 16-BIT) CACHED DRAM WITH 16K (1024-WORD BY 16-BIT) SRAM |

| M5M4V16169DTP-10 | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:16MCDRAM:16M(1M-WORD BY 16-BIT) CACHED DRAM WITH 16K (1024-WORD BY 16-BIT) SRAM |

| M5M4V16169DTP-15 | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:16MCDRAM:16M(1M-WORD BY 16-BIT) CACHED DRAM WITH 16K (1024-WORD BY 16-BIT) SRAM |

| M5M4V16169DTP-7 | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:16MCDRAM:16M(1M-WORD BY 16-BIT) CACHED DRAM WITH 16K (1024-WORD BY 16-BIT) SRAM |

| M5M4V16169DTP-8 | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:16MCDRAM:16M(1M-WORD BY 16-BIT) CACHED DRAM WITH 16K (1024-WORD BY 16-BIT) SRAM |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。