- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄45037 > M37735MHBXXXFP 16-BIT, MROM, 25 MHz, MICROCONTROLLER, PQFP80 PDF資料下載

參數(shù)資料

| 型號(hào): | M37735MHBXXXFP |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 16-BIT, MROM, 25 MHz, MICROCONTROLLER, PQFP80 |

| 封裝: | 14 X 20 MM, 0.80 MM PITCH, PLASTIC, QFP-80 |

| 文件頁數(shù): | 22/93頁 |

| 文件大小: | 1802K |

| 代理商: | M37735MHBXXXFP |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁當(dāng)前第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁

26

MITSUBISHI MICROCOMPUTERS

M37735MHBXXXFP

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

PRELIMINAR

Y

Notice:

This

is not

a final

specification.

Some

parametric

limits

are

subject

to change.

TIMER B

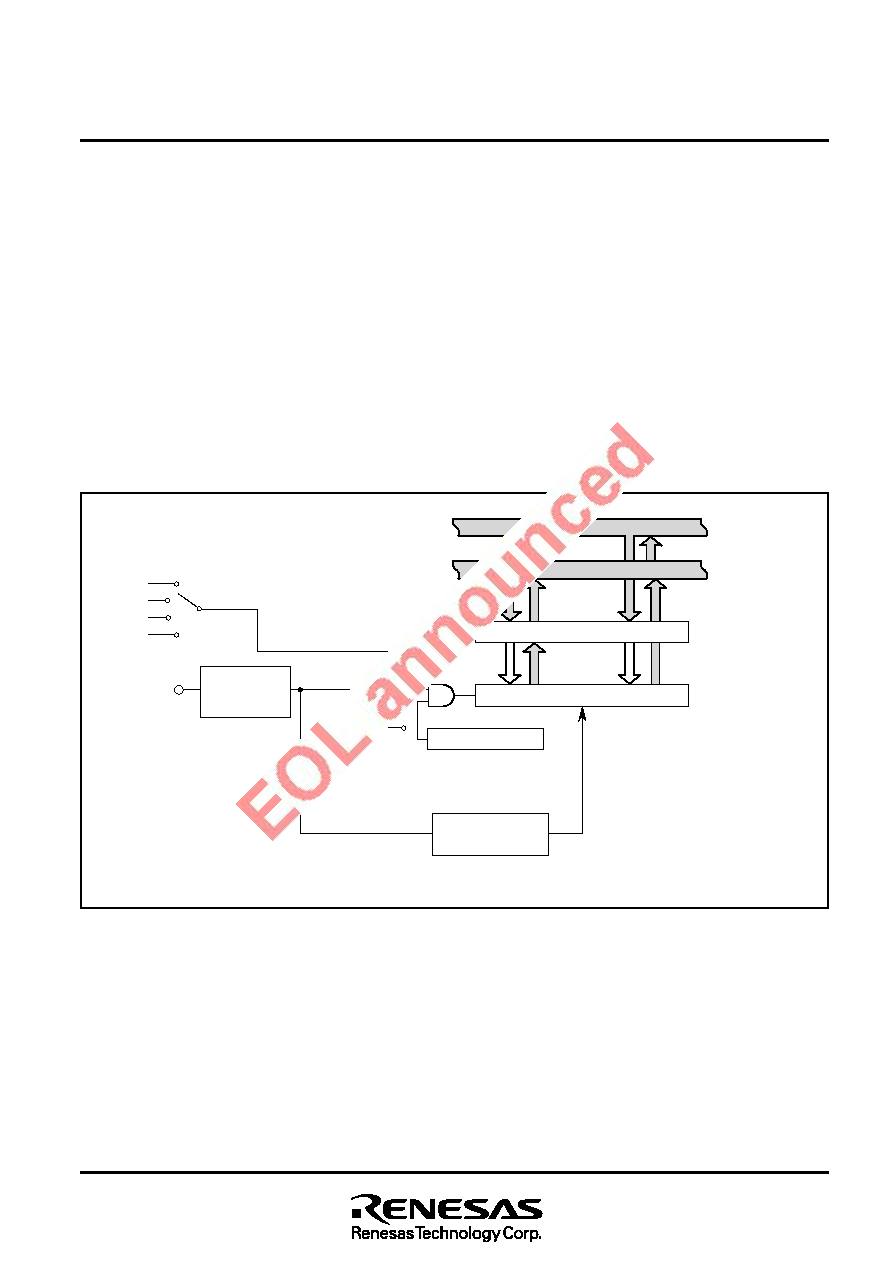

Figure 29 shows a block diagram of timer B.

Timer B has three modes; timer mode, event counter mode, and

pulse period measurement/pulse width measurement mode. The

mode is selected with bits 0 and 1 of the timer Bi mode register (i = 0

to 2). Timer B2 can also be used as the clock timer of which clock

source is the main clock or the sub-clock divided by 32. Additionally,

timer B2 can be internally connected to timer B1 (cascade connection).

Each of these modes is described below.

(1) Timer mode [00]

Figure 30 shows the bit configuration of the timer Bi mode register

during the timer mode. Bits 0 and 1 of the timer Bi mode register

must always be “0” in the timer mode.

Bits 6 and 7 are used to select the clock source. The counting of the

selected clock starts when the count start flag is “1” and stops when

it is “0”.

As shown in Figure 15, the timer Bi count start flag is at the same

address as the timer Ai count start flag. The count is decremented.

When the contents of the counter becomes 000016, an interrupt

request occurs and the interrupt request bit of the timer Bi interrupt

control register is set. At the same time, the contents of the reload

register is stored in the counter, and count is continued.

Timer Bi does not have a pulse output function or a gate function like

timer A.

When data is written to timer Bi halted, it is written to the reload register

and the counter. When data is written to timer Bi which is busy, the

data is written to the reload register, but not to the counter. The counter

is reloaded with new data from the reload register at the next reload

time and continues counting. The contents of the counter can be

read at any time.

Fig. 29 Timer B block diagram

Notes 1. Clock source of clock timer; Only Timer B2 can select it (refer to Fig. 65)

2. Only Timer B1 can select it (internal connect mode)

f2

f16

f64

f512

Timer

Pulse period measurement/pulse

width measurement

Polarity selection

and edge pulse

generator

Event counter

Count start flag

Addresses

Timer B0 5116 5016

Timer B1 5316 5216

Timer B2 5516 5416

TBi IN

(i = 0 – 2)

(Address 4016)

Counter reset

circuit

Clock source selection

Data bus (odd)

(Low-order 8 bits)

Data bus (even)

(High-order 8 bits)

Counter (16)

Reload register (16)

fC32 (Note 1)

TB2 overflow

signal (Note 2)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M37735MHLXXXHP | 16-BIT, MROM, 12 MHz, MICROCONTROLLER, PQFP80 |

| M37735S4LHP | 16-BIT, 12 MHz, MICROCONTROLLER, PQFP80 |

| M37736EHBGS | 16-BIT, UVPROM, 24 MHz, MICROCONTROLLER, CQCC100 |

| M37736EHBXXXGP | 16-BIT, OTPROM, 25 MHz, MICROCONTROLLER, PQFP100 |

| M37736EHBGS | 16-BIT, UVPROM, 25 MHz, MICROCONTROLLER, CQCC100 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M37735MHL | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER |

| M37735MHL-143HP | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:PROM VERSION OF M37735MHLXXXHP |

| M37735MHLXXXHP | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER |

| M37735S4BFP | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:16-BIT CMOS MICROCOMPUTER |

| M37735S4LHP | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:16-BIT CMOS MICROCOMPUTER |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。