- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄69010 > M34280E1GP 4-BIT, OTPROM, 4 MHz, MICROCONTROLLER, PDSO20 PDF資料下載

參數(shù)資料

| 型號(hào): | M34280E1GP |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 4-BIT, OTPROM, 4 MHz, MICROCONTROLLER, PDSO20 |

| 封裝: | 0.225 INCH, 0.65 MM PITCH, PLASTIC, SSOP-20 |

| 文件頁(yè)數(shù): | 39/48頁(yè) |

| 文件大?。?/td> | 605K |

| 代理商: | M34280E1GP |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)當(dāng)前第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)

Interrupt

Mitsubishi microcomputers

M16C / 62N Group (80-pin)

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

43

Interrupt Enable Flag (I flag)

The interrupt enable flag (I flag) controls the enabling and disabling of maskable interrupts. Setting this

flag to “1” enables all maskable interrupts; setting it to “0” disables all maskable interrupts. This flag is set

to “0” after reset.

Interrupt Request Bit

The interrupt request bit is set to "1" by hardware when an interrupt is requested. After the interrupt is

accepted and jumps to the corresponding interrupt vector, the request bit is set to "0" by hardware. The

interrupt request bit can also be set to "0" by software. (Do not set this bit to "1").

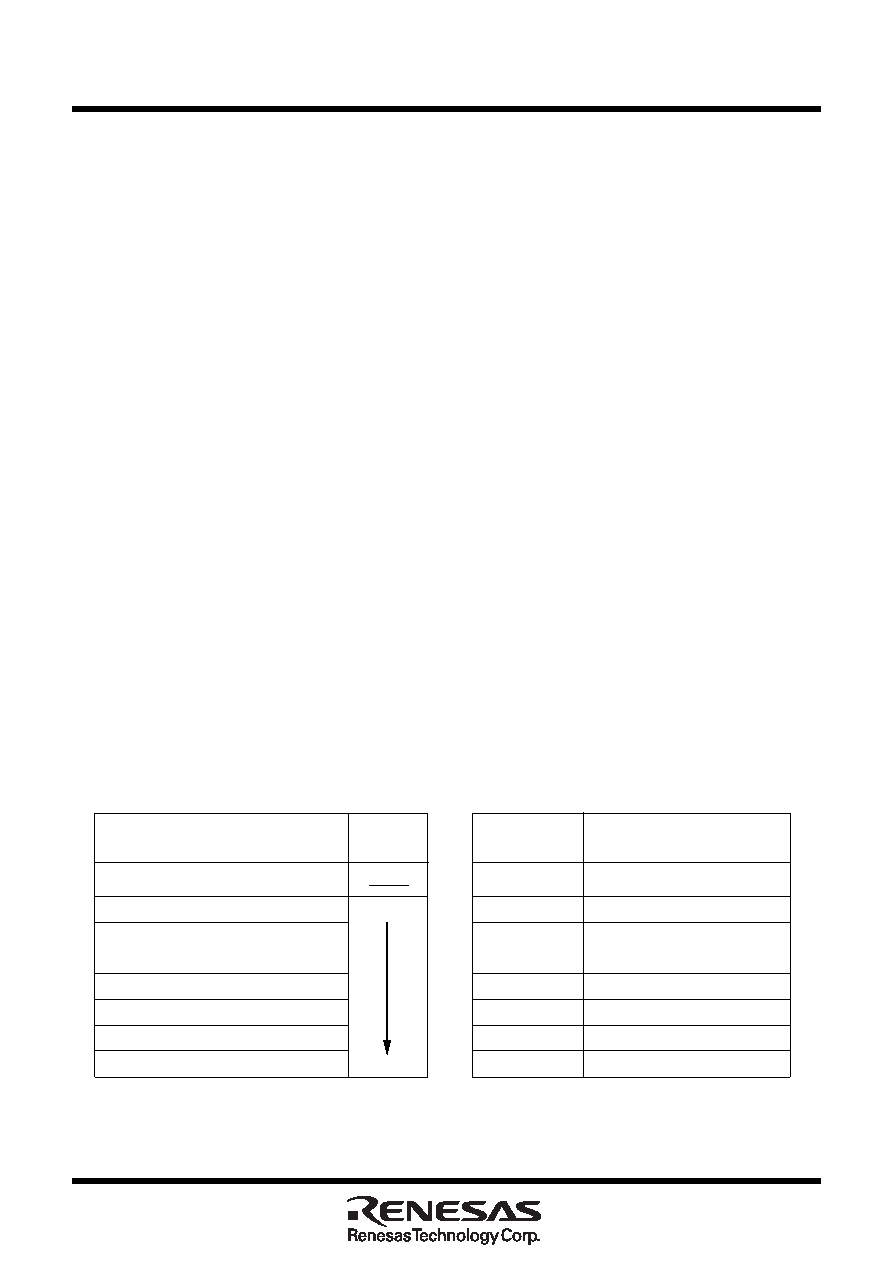

Table 1.10.4. Interrupt levels enabled according

to the contents of the IPL

Table 1.10.3. Settings of interrupt priority

levels

Interrupt priority

level select bit

Interrupt priority

level

Priority

order

0

1

0

1

0

1

0

1

0

1

0

1

Level 0 (interrupt disabled)

Level 1

Level 2

Level 3

Level 4

Level 5

Level 6

Level 7

Low

High

b2 b1 b0

Enabled interrupt priority levels

0

1

0

1

0

1

0

1

0

1

0

1

Interrupt levels 1 and above are enabled

Interrupt levels 2 and above are enabled

Interrupt levels 3 and above are enabled

Interrupt levels 4 and above are enabled

Interrupt levels 5 and above are enabled

Interrupt levels 6 and above are enabled

Interrupt levels 7 and above are enabled

All maskable interrupts are disabled

IPL2 IPL1 IPL0

IPL

Interrupt Priority Level Select Bit and Processor Interrupt Priority Level (IPL)

Set the interrupt priority level using the interrupt priority level select bit, which is one of the component bits

of the interrupt control register. When an interrupt request occurs, the interrupt priority level is compared

with the IPL. The interrupt is enabled only when the priority level of the interrupt is higher than the IPL.

Therefore, setting the interrupt priority level to “0” disables the interrupt.

Table 1.10.3 shows the settings of interrupt priority levels and Table 1.10.4 shows the interrupt levels

enabled, according to the contents of the IPL.

The following are conditions under which an interrupt is accepted:

interrupt enable flag (I flag) = 1

interrupt request bit = 1

interrupt priority level > IPL

The interrupt enable flag (I flag), the interrupt request bit, the interrupt priority select bit, and the IPL are

independent, and they are not affected by one another.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M34501M2-XXXFP | 4-BIT, MROM, 4.4 MHz, MICROCONTROLLER, PDSO20 |

| M34501E4FP | 4-BIT, OTPROM, 4.4 MHz, MICROCONTROLLER, PDSO20 |

| M34501M2-XXXFP | 4-BIT, MROM, MICROCONTROLLER, PDSO20 |

| M34501E4FP | 4-BIT, OTPROM, MICROCONTROLLER, PDSO20 |

| M34501M4-XXXFP | 4-BIT, MROM, MICROCONTROLLER, PDSO20 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M34280M1 | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER for INFRARED REMOTE CONTROL TRANSMITTERS |

| M34280M1-060FP | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER for INFRARED REMOTE CONTROL TRANSMITTERS |

| M34280M1-082GP | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER for INFRARED REMOTE CONTROL TRANSMITTERS |

| M34280M1-089FP | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER for INFRARED REMOTE CONTROL TRANSMITTERS |

| M34280M1-105FP | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER for INFRARED REMOTE CONTROL TRANSMITTERS |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。