- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377800 > M12L128324A (Elite Semiconductor Memory Technology Inc.) 1M x 32 Bit x 4 Banks Synchronous DRAM PDF資料下載

參數(shù)資料

| 型號(hào): | M12L128324A |

| 廠商: | Elite Semiconductor Memory Technology Inc. |

| 英文描述: | 1M x 32 Bit x 4 Banks Synchronous DRAM |

| 中文描述: | 100萬× 32位× 4個(gè)銀行同步DRAM |

| 文件頁數(shù): | 41/47頁 |

| 文件大?。?/td> | 794K |

| 代理商: | M12L128324A |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁當(dāng)前第41頁第42頁第43頁第44頁第45頁第46頁第47頁

ES MT

M12L128324A

Elite Semiconductor Memory Technology Inc.

Publication Date: Mar. 2006

Revision

:

1.2

41/47

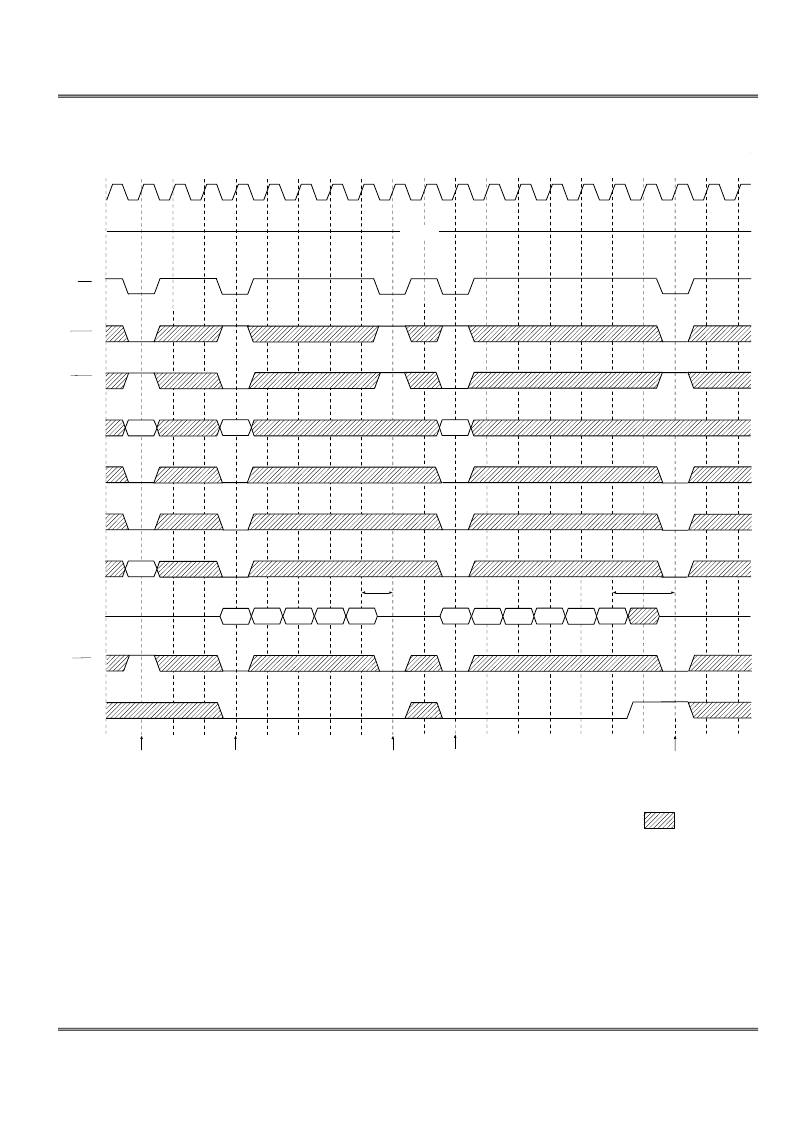

Write interrupted by Precharge Command & Write Burst Stop Cycle @ Burst Length = Full page

*Note : 1. Data-in at the cycle of interrupted by precharge can not be written into the corresponding memory cell. It is defined by

AC parameter of t

RDL

.

DQM at write interrupted by precharge command is needed to prevent invalid write.

DQM should mask invalid input data on precharge command cycle when asserting precharge before end of burst. Input

data after Row precharge cycle will be masked internally.

2. Burst stop is valid at every burst length.

C L O C K

C K E

C S

R A S

C A S

A D D R

W E

DQ

DQ M

A10/AP

BA1

BA0

RAa

CAa

CAb

RAa

DAa0 DAa1

DAb1

DAb0

DAb2

Row Active

(A-Bank)

W rite

(A-Bank)

Burst Stop

W rite

(A-Bank)

:Don't Care

HIGH

DAa2 DAa3 DAa4

DAb3 DAb4 DAb5

Precharge

(A-Bank)

t

B D L

t

RD L

* Not e 1

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M12L128324A-6BG | 1M x 32 Bit x 4 Banks Synchronous DRAM |

| M12L128324A-6TG | 1M x 32 Bit x 4 Banks Synchronous DRAM |

| M12L16161A-5TG | 512K x 16Bit x 2Banks Synchronous DRAM |

| M12L16161A-7BG | 512K x 16Bit x 2Banks Synchronous DRAM |

| M12L16161A-7TG | 512K x 16Bit x 2Banks Synchronous DRAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M12L128324A_09 | 制造商:ESMT 制造商全稱:Elite Semiconductor Memory Technology Inc. 功能描述:1M x 32 Bit x 4 Banks Synchronous DRAM |

| M12L128324A_1 | 制造商:ESMT 制造商全稱:Elite Semiconductor Memory Technology Inc. 功能描述:1M x 32 Bit x 4 Banks Synchronous DRAM |

| M12L128324A2E | 制造商:ESMT 制造商全稱:Elite Semiconductor Memory Technology Inc. 功能描述:JEDEC standard 3.3V power supply |

| M12L128324A-5BG2E | 制造商:ESMT 制造商全稱:Elite Semiconductor Memory Technology Inc. 功能描述:JEDEC standard 3.3V power supply |

| M12L128324A-6BG | 制造商:ESMT 制造商全稱:Elite Semiconductor Memory Technology Inc. 功能描述:1M x 32 Bit x 4 Banks Synchronous DRAM |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。