- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377800 > M12L128168A-5TG (ELITE SEMICONDUCTOR MEMORY TECHNOLOGY INC) 2M x 16 Bit x 4 Banks Synchronous DRAM PDF資料下載

參數(shù)資料

| 型號(hào): | M12L128168A-5TG |

| 廠商: | ELITE SEMICONDUCTOR MEMORY TECHNOLOGY INC |

| 元件分類: | DRAM |

| 英文描述: | 2M x 16 Bit x 4 Banks Synchronous DRAM |

| 中文描述: | 8M X 16 SYNCHRONOUS DRAM, 4.5 ns, PDSO54 |

| 封裝: | 0.400 INCH, LEAD FREE, TSOP2-54 |

| 文件頁數(shù): | 13/43頁 |

| 文件大小: | 804K |

| 代理商: | M12L128168A-5TG |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁當(dāng)前第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁

ESMT

M12L128168A

Elite Semiconductor Memory Technology Inc.

Revision

:

2.0

Publication Date

:

Oct. 2006

13/43

COMMANDS

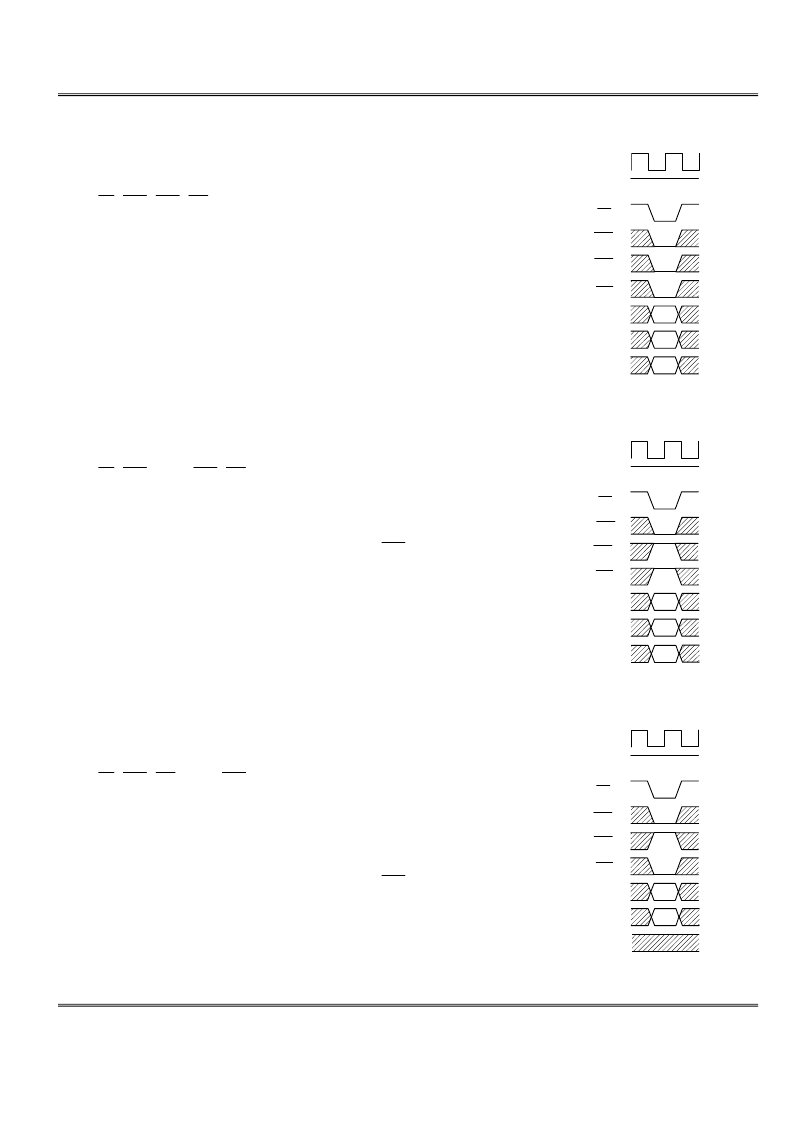

Mode register set command

(CS ,RAS ,CAS ,

WE

= Low)

The M12L128168A has a mode register that defines how the device operates. In

this command, A0 through A13 are the data input pins. After power on, the mode

register set command must be executed to initialize the device.

The mode register can be set only when all banks are in idle state.

During 2CLK following this command, the M12L128168A cannot accept any

other commands.

Activate command

(CS ,RAS = Low,CAS ,

WE

= High)

The M12L128168A has four banks, each with 4,096 rows.

This command activates the bank selected by A12 and A13 (BS) and a row

address selected by A0 through A11.

This command corresponds to a conventional DRAM’s RAS falling.

Precharge command

(CS ,RAS ,

WE

= Low,CAS = High )

This command begins precharge operation of the bank selected by A12 and A13

(BS). When A10 is High, all banks are precharged, regardless of A12 and A13. When

A10 is Low, only the bank selected by A12 and A13 is precharged.

After this command, the M12L128168A can’t accept the activate command to the

precharging bank during t

RP

(precharge to activate command period).

This command corresponds to a conventional DRAM’s RAS rising.

CLK

CLK

CKE

CKE

CS

CS

RAS

RAS

WE

WE

A12, A13

A12, A13

(Bank select)

A10

A10

Add

Add

CAS

CAS

H

H

Row

Row

Fig. 1 Mode register set

command

Fig. 2 Row address strobe and

bank active command

CLK

CKE

CS

RAS

WE

A12, A13

(Bank select)

A10

(Precharge select)

Add

CAS

H

Fig. 3 Precharge command

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M12L128168A-6TG | 2M x 16 Bit x 4 Banks Synchronous DRAM |

| M12L128168A-7TG | 2M x 16 Bit x 4 Banks Synchronous DRAM |

| M12L128324A-7BG | 1M x 32 Bit x 4 Banks Synchronous DRAM |

| M12L128324A-7TG | 1M x 32 Bit x 4 Banks Synchronous DRAM |

| M12L128324A | 1M x 32 Bit x 4 Banks Synchronous DRAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M12L128168A-5TG2L | 制造商:ESMT 制造商全稱:Elite Semiconductor Memory Technology Inc. 功能描述:ABSOLUTE MAXIMUM RATINGS |

| M12L128168A-5TIG | 制造商:ESMT 制造商全稱:Elite Semiconductor Memory Technology Inc. 功能描述:2M x 16 Bit x 4 Banks Synchronous DRAM |

| M12L128168A-6BG | 制造商:ESMT 制造商全稱:Elite Semiconductor Memory Technology Inc. 功能描述:2M x 16 Bit x 4 Banks Synchronous DRAM |

| M12L128168A-6BG2L | 制造商:ESMT 制造商全稱:Elite Semiconductor Memory Technology Inc. 功能描述:ABSOLUTE MAXIMUM RATINGS |

| M12L128168A-6BIG | 制造商:ESMT 制造商全稱:Elite Semiconductor Memory Technology Inc. 功能描述:2M x 16 Bit x 4 Banks Synchronous DRAM |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。