- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄378652 > LXT974 (Intel Corp.) Fast Ethernet 10/100 Quad Transceivers PDF資料下載

參數(shù)資料

| 型號: | LXT974 |

| 廠商: | Intel Corp. |

| 英文描述: | Fast Ethernet 10/100 Quad Transceivers |

| 中文描述: | 四10/100快速以太網(wǎng)收發(fā)器 |

| 文件頁數(shù): | 17/74頁 |

| 文件大?。?/td> | 1089K |

| 代理商: | LXT974 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁當(dāng)前第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁

Fast Ethernet 10/100 Quad Transceivers

—

LXT974/LXT975

Datasheet

17

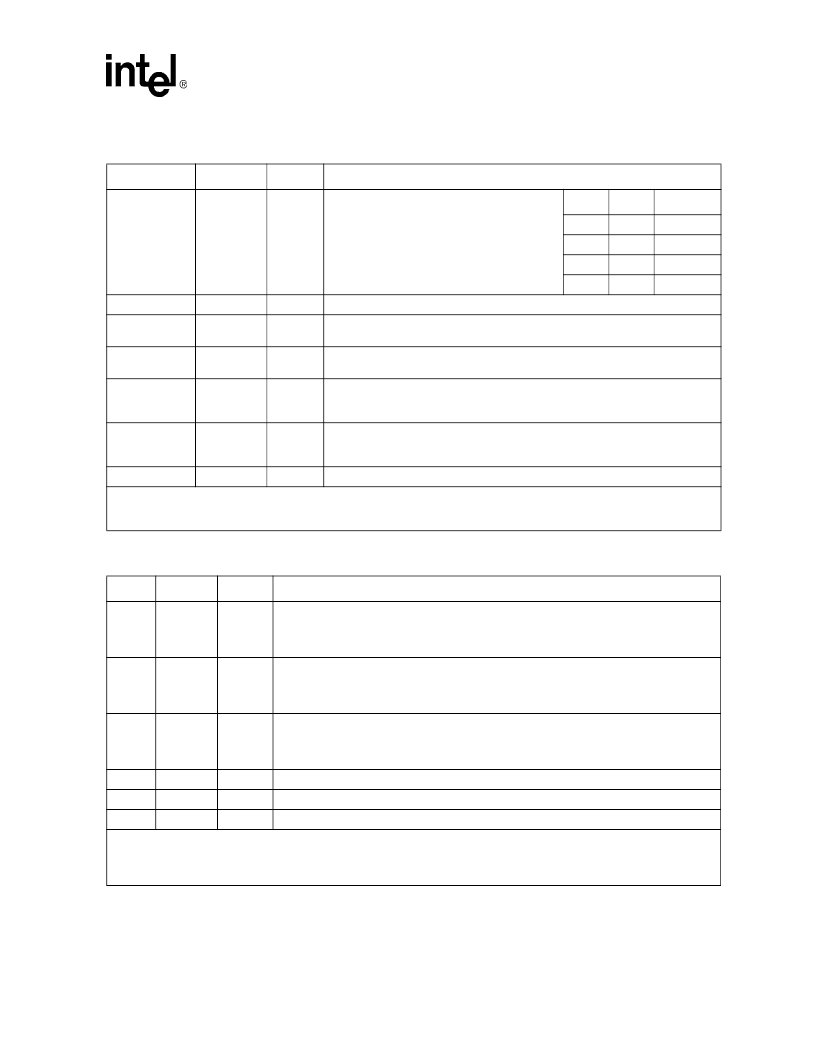

Table 9. LXT974 and LXT975 Miscellaneous Signal Descriptions

Pin#

Symbol

Type

1

Signal Description

2

20

19

18

ADD4

ADD3

ADD2

I

I

I

Address <4:2>

. Set upper three bits of PHY

address. ADD<1:0> are set internally to match

port number as shown at right.

ADD1

ADD0

Port

0

0

0

0

1

1

1

0

2

1

1

3

101, 112, 159

TEST

I

Test.

Must be tied Low.

140

RBIAS

I

Bias

. This pin provides bias current for the internal circuitry. Must be tied to

ground through a 22 k

resistor.

Clock Input

. A 25 MHz clock input is required at this pin. Refer to Functional

Description for detailed clock requirements.

118

CLK25M

I

109

RESET

I

Reset

. This active Low input is OR

’

ed with the control register Reset bit (0.15).

The LXT974/975 reset cycle is extended 205

μ

s (nominal) after Reset is de-

asserted.

102

PWRDN

I

Power Down

. When High, forces LXT974/975 into power down mode. This pin is

OR

’

ed with the Power Down bit (0.11). Refer to

Table 44 on page 64

for more

information.

41, 119, 120

N/C

-

No Connection

.

Leave open.

1. Type Column Coding: I = Input, O = Output, A = Analog.

2. The LXT974/975 supports the 802.3 MDIO register set. Specific bits in the registers are referenced using an

“

X.Y

”

notation,

where X is the register number (0-6 or 16-20) and Y is the bit number (0-15).

Table 10. LXT974 and LXT975 LED Indicator Signal Descriptions

Pin#

2

Symbol

Type

1

Signal Description

3

11

8

4

1

LED0_0

LED1_0

LED2_0

LED3_0

OD

LED0 - Ports 0 - 3

. In default mode, active Low output indicates transmitter active. However,

LED0 is programmable and may also be set to indicate receiver active, link status or duplex

status. Refer to LED Configuration Register,

Table 51 on page 68

, for details on

programming options.

12

9

5

2

LED0_1

LED1_1

LED2_1

LED3_1

OD

LED1 - Ports 0 - 3

. In default mode, active Low output indicates receiver active. However,

LED1 is programmable and may also be set to indicate link status, duplex status, or operating

speed. Refer to LED Configuration Register,

Table 51 on page 68

, for details on

programming options.

13

10

6

3

LED0_2

LED1_2

LED2_2

LED3_2

OD

LED2 - Ports 0 - 3

. In default mode, active Low output indicates link up. However, LED2 is

programmable and may also be set to indicate duplex status, operating speed or collision.

Refer to LED Configuration Register,

Table 51 on page 68

, for details on

programming options.

17

LEDENA

O

LED Enable.

Active High output signals external device that LEDDAT is active.

15

LEDCLK

O

LED Clock.

25 MHz clock for LED serial data output.

16

LEDDAT

O

LED Data.

Serial data output for 24 LEDs (6 x 4 ports) data.

1. Type Column Coding: I = Input, O = Output, OD = Open Drain.

2. Unused pins should be tied Low.

3. The LXT974/975 supports the 802.3 MDIO register set. Specific bits in the registers are referenced using an

“

X.Y

”

notation,

where X is the register number (0-6 or 16-20) and Y is the bit number (0-15).

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LXT974A | Fast Ethernet 10/100 Quad Transceivers |

| LXT974AHC | Fast Ethernet 10/100 Quad Transceivers |

| LXT974B | Fast Ethernet 10/100 Quad Transceivers |

| LXT974BHC | Fast Ethernet 10/100 Quad Transceivers |

| LXT975 | Fast Ethernet 10/100 Quad Transceivers |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LXT974A | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Fast Ethernet 10/100 Quad Transceivers |

| LXT974AHC | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Fast Ethernet 10/100 Quad Transceivers |

| LXT974B | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Fast Ethernet 10/100 Quad Transceivers |

| LXT974BHC | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Fast Ethernet 10/100 Quad Transceivers |

| LXT974QC | 制造商:LEVELONE 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。