- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄378652 > LXT974 (Intel Corp.) Fast Ethernet 10/100 Quad Transceivers PDF資料下載

參數(shù)資料

| 型號: | LXT974 |

| 廠商: | Intel Corp. |

| 英文描述: | Fast Ethernet 10/100 Quad Transceivers |

| 中文描述: | 四10/100快速以太網(wǎng)收發(fā)器 |

| 文件頁數(shù): | 13/74頁 |

| 文件大小: | 1089K |

| 代理商: | LXT974 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁當(dāng)前第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁

Fast Ethernet 10/100 Quad Transceivers

—

LXT974/LXT975

Datasheet

13

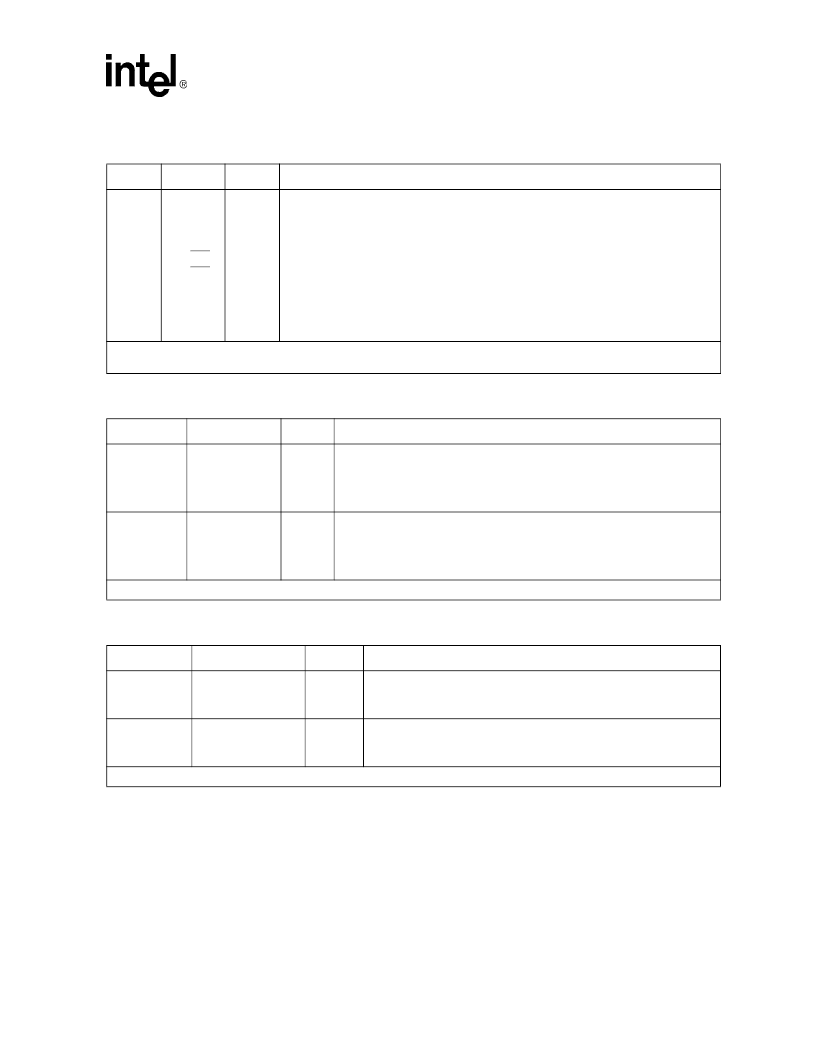

Table 4. LXT975 Signal Detect/TP Select Signal Descriptions

Pin#

2

Symbol

Type

1

Signal Description

149

130

SD1/TP1

SD3/TP3

I

Signal Detect - Ports 1 & 3

. When SD/TP

n

pins are tied High or to a 5V PECL input, bit

19.2 = 1 and the operating mode of each respective port is forced to FX mode. In this

mode, full-duplex is set via pin 117 (FDE_FX). When not using fiber mode, SD/TP

n

pins

should be tied to GNDT.

TP Select - Ports 1 & 3

. When SD/TP

n

pins are tied Low, bit 19.2 = 0. The operating mode

of each port can be set to 10BASE-T, 100BASE-TX, or 100BASE-FX via the hardware

control interface pins as shown in

Table 8 on page 16

.

Note: Hardware control interface pins (CFG_0, CFG_1, CFG_2, FDE, BYPSCR, and

AUTOENA) are global and set all ports simultaneously.

In TP mode, network pins operate as described in

Table 5

.

In FX mode, network pins are re-mapped and operate as described in

Table 6

.

1. Type Column Coding: I = Input, O = Output.

2. When not using fiber mode, SD/TP

n

pins should be tied to GNDT.

Table 5. LXT975 Twisted-Pair Interface Signal Descriptions

Pin#

Symbol

Type

1

Signal Description

155, 152

145, 148

136, 133

126, 129

TPOP0, TPON0

TPOP1, TPON1

TPOP2, TPON2

TPOP3, TPON3

O

Twisted-Pair Outputs, Positive & Negative - Ports 0-3.

During 100BASE-TX or 10BASE-T operation, TPO pins drive 802.3 compliant

pulses onto the line.

158, 157

142, 143

139, 138

123, 124

TPIP0, TPIN0

TPIP1, TPIN1

TPIP2, TPIN2

TPIP3, TPIN3

I

Twisted-Pair Inputs, Positive & Negative - Ports 0-3.

During 100BASE-TX or 10BASE-T operation, TPI pins receive differential

100BASE-TX or 10BASE-T signals from the line.

1. Type Column Coding: I = Input, O = Output.

Table 6. LXT975 Fiber Interface Signal Descriptions

Pin#

Symbol

Type

1

Signal Description

145, 148

126, 129

FIBIN1, FIBIP1

FIBIN3, FIBIP3

I

Fiber Network Interface - Ports 1 and 3

During 100BASE-FX operation, FIBI pins receive differential PECL inputs

from fiber transceivers.

142, 143

123, 124

FIBOP1, FIBON1

FIBOP3, FIBON3

O

Fiber Network Interface - Ports 1 and 3

During 100BASE-FX operation, FIBO pins produce differential PECL

outputs for fiber transceivers.

1. Type Column Coding: I = Input, O = Output.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LXT974A | Fast Ethernet 10/100 Quad Transceivers |

| LXT974AHC | Fast Ethernet 10/100 Quad Transceivers |

| LXT974B | Fast Ethernet 10/100 Quad Transceivers |

| LXT974BHC | Fast Ethernet 10/100 Quad Transceivers |

| LXT975 | Fast Ethernet 10/100 Quad Transceivers |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LXT974A | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Fast Ethernet 10/100 Quad Transceivers |

| LXT974AHC | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Fast Ethernet 10/100 Quad Transceivers |

| LXT974B | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Fast Ethernet 10/100 Quad Transceivers |

| LXT974BHC | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Fast Ethernet 10/100 Quad Transceivers |

| LXT974QC | 制造商:LEVELONE 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。