- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄358809 > LM1253AN (NATIONAL SEMICONDUCTOR CORP) Monolithic Triple 180 MHz I2C CRT Pre-amp With Integrated Analog On Screen Display (OSD) Generator PDF資料下載

參數(shù)資料

| 型號(hào): | LM1253AN |

| 廠商: | NATIONAL SEMICONDUCTOR CORP |

| 元件分類: | 畫面疊加 |

| 英文描述: | Monolithic Triple 180 MHz I2C CRT Pre-amp With Integrated Analog On Screen Display (OSD) Generator |

| 中文描述: | ON-SCREEN DISPLAY IC, PDIP28 |

| 封裝: | 0.600 INCH, PLASTIC, DIP-28 |

| 文件頁數(shù): | 40/57頁 |

| 文件大小: | 1621K |

| 代理商: | LM1253AN |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁當(dāng)前第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁

Control Register Definitions

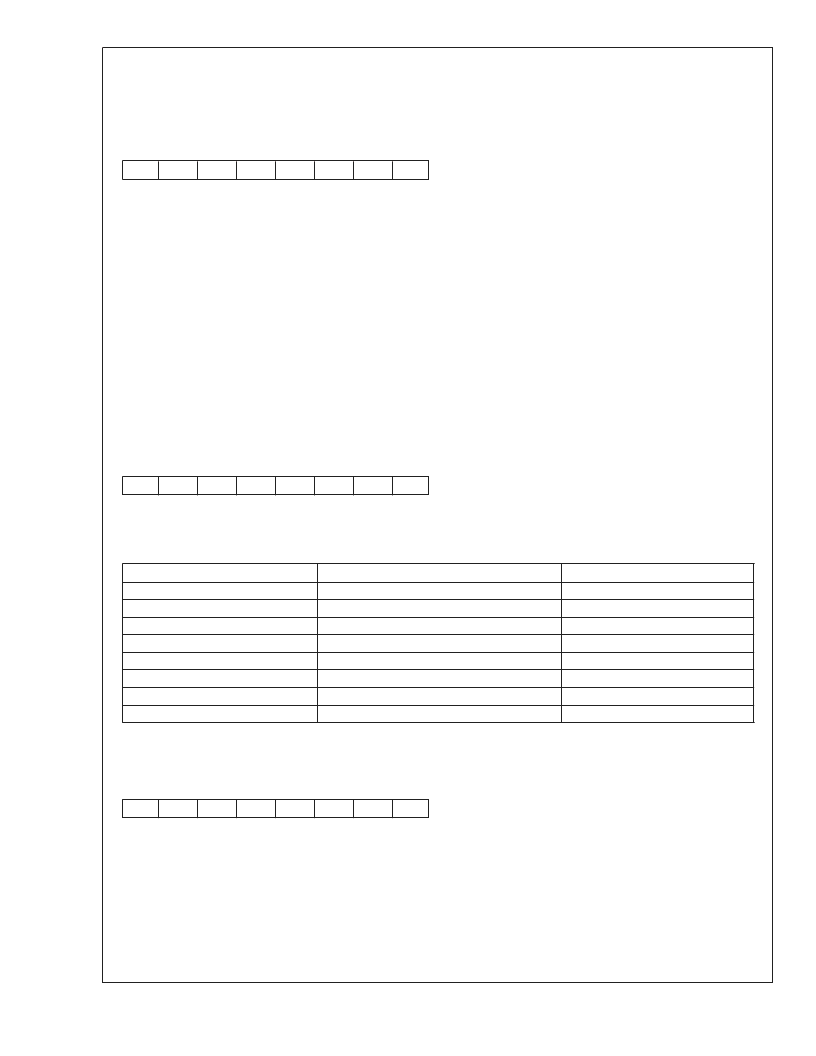

OSD INTERFACE REGISTERS

Frame Control Register 1 (I

2

C address 8400h).

REGISTER NAME: FRMCTRL1

Bit 7

Bit 0

RSV

RSV

RSV

TD

CDPR

D2E

D1E

OsE

Bit 0:

On-Screen Display Enable. The On-Screen Display will be disabled when this bit is a zero. When this bit is a one the

On-Screen Display will be enabled and Display Window 1 will be enabled if Bit 1 of this register is a one; likewise Dis-

play Window 2 will be enabled if Bit 2 of this register is a one.

Display Window 1 Enable. When Bit 0 of this register and this bit are both ones, Display Window 1 is enabled. If either

bit is a zero, then Display Window 1 will be disabled.

Display Window 2 Enable. When Bit 0 of this register and this bit are both ones, Display Window 2 is enabled. If either

bit is a zero, then Display Window 2 will be disabled.

Clear Display Page RAM. Writing a one to this bit will result in setting all of the Display Page RAM values to zero. This

bit is automatically cleared after the operation is complete.

Transparent Disable. When this bit is a zero, a palette color of black (ie color palette look-up table value of ‘000 000

000’) in the first 8 palette look-up table address locations (i.e., ATT = 0h–7h) will be translated as transparent. When

this bit is a one, the color will be translated as black.

Bits 7–4: RESERVED.

Bit 1:

Bit 2:

Bit 3:

Bit 4:

Frame Control Register 2 (I

2

C address 8401h).

REGISTER NAME: FRMCTRL2

Bit 7

Bit 0

PL2

PL1

PL0

BP4

BP3

BP2

BP1

BP0

Bits 4–0: Blinking Period. These five bits set the blinking period of the blinking feature, which is determined by multiplying the

value of these bits by 8, and then multiplying the result by the vertical field rate.

Bits 7–5: Pixels per Line. These three bits determine the number of pixels per line.

Bits 7–5

000b

001b

010b

011b

100b

101b

110b

111b

Description

512 pixels per line

576 pixels per line

640 pixels per line

704 pixels per line

768 pixels per line

832 pixels per line

896 pixels per line

960 pixels per line

Max Fh

125 kHz

119 kHz

112 kHz

106 kHz

100 kHz

93 kHz

87 kHz

81 kHz

Character Font Access Control Register (I

2

C address 8402h).

REGISTER NAME: CHARFONTACC

Bit 7

Bit 0

RSV

RSV

RSV

RSV

RSV

RSV

C/A

Bit

Bit 0:

Four-color pixel data value Bit indicator. This bit indicates if Bit 0 (when a zero) or Bit 1 (when a one) of the four-color

pixel data value is being accessed via I

2

C addresses 3000h–3FFFh.

Character/Attribute Code Indicator. This bit controls what value is read via I

2

C reads of the Display Page RAM (ad-

dress range 8000h–81FFh). When this bit is a 0, such reads will return the character code. When this bit is a 1, the

attribute code will be returned.

Bits 7–2: RESERVED.

Bit 1:

L

www.national.com

40

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LM1253A | Monolithic Triple 180 MHz I2C CRT Pre-amp With Integrated Analog On Screen Display (OSD) Generator |

| LM1262 | 200 MHz I2C Compatible RGB Video Amplifier System with OSD and DACs |

| LM1262NA | 200 MHz I2C Compatible RGB Video Amplifier System with OSD and DACs |

| LM1267NA | 150 MHz I2C Compatible RGB Video Amplifier System with OSD and DACs |

| LM1267 | 150 MHz I2C Compatible RGB Video Amplifier System with OSD and DACs |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LM-1256 | 制造商:ROHM 制造商全稱:Rohm 功能描述:16 x 16 matrix displays |

| LM-1256_1 | 制造商:ROHM 制造商全稱:Rohm 功能描述:16】16 matrix displays |

| LM-1256LB1 | 制造商:ROHM 制造商全稱:Rohm 功能描述:16】16 matrix displays |

| LM125AN | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:VOLTAGE REGULATORS |

| LM125H | 制造商: 功能描述: 制造商:undefined 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。