- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄377610 > LC4384x (Lattice Semiconductor Corporation) 3.3V/2.5V/1.8V In-System Programmable SuperFAST High density PDLs PDF資料下載

參數(shù)資料

| 型號(hào): | LC4384x |

| 廠商: | Lattice Semiconductor Corporation |

| 英文描述: | 3.3V/2.5V/1.8V In-System Programmable SuperFAST High density PDLs |

| 中文描述: | 3.3V/2.5V/1.8V在系統(tǒng)可編程超快高密度PDLs |

| 文件頁(yè)數(shù): | 23/91頁(yè) |

| 文件大小: | 851K |

| 代理商: | LC4384X |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)當(dāng)前第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)

Lattice Semiconductor

ispMACH 4000V/B/C/Z Family Data Sheet

23

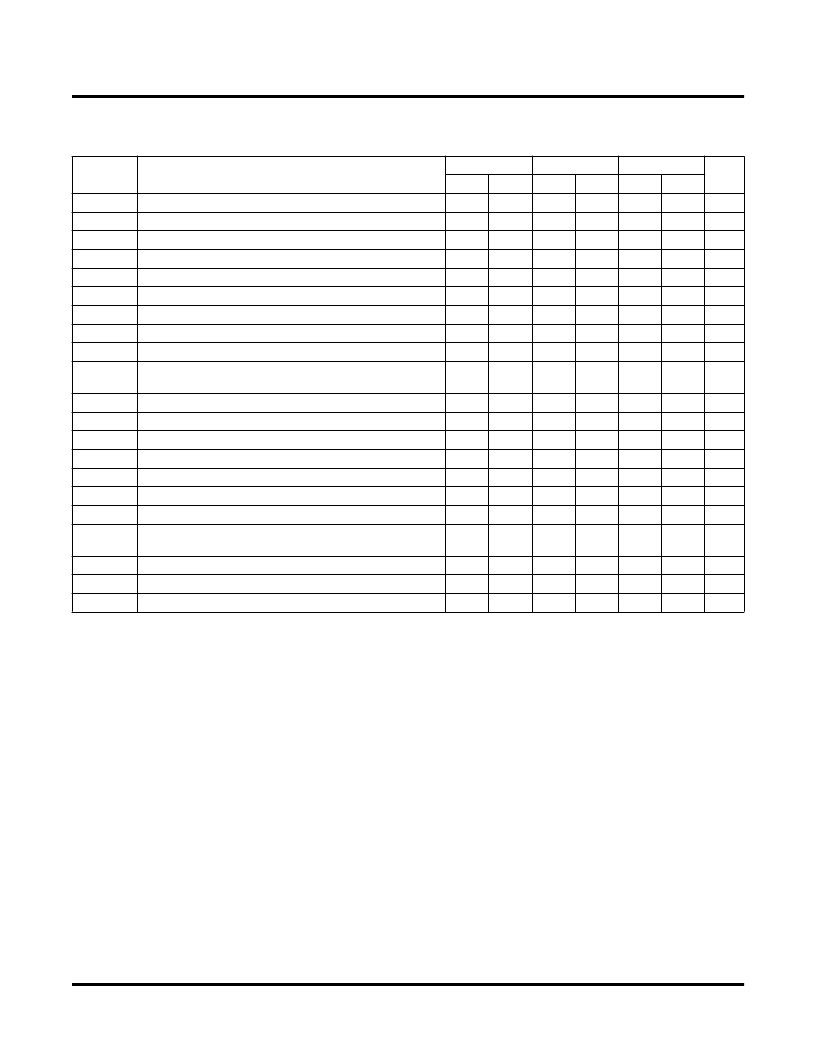

ispMACH 4000V/B/C External Switching Characteristics (Cont.)

Over Recommended Operating Conditions

Parameter

Description

1, 2, 3

-5

-75

-10

Units

Min.

Max.

Min.

Max.

Min.

Max.

t

PD

t

PD_MC

t

S

t

ST

t

SIR

t

SIRZ

t

H

t

HT

t

HIR

5-PT bypass combinatorial propagation delay

—

5.0

—

7.5

—

10.0

ns

20-PT combinatorial propagation delay through macrocell

—

5.5

—

8.0

—

10.5

ns

GLB register setup time before clock

3.0

—

4.5

—

5.5

—

ns

GLB register setup time before clock with T-type register

3.2

—

4.7

—

5.5

—

ns

GLB register setup time before clock, input register path

1.2

—

1.7

—

1.7

—

ns

GLB register setup time before clock with zero hold

2.2

—

2.7

—

2.7

—

ns

GLB register hold time after clock

0.0

—

0.0

—

0.0

—

ns

GLB register hold time after clock with T-type register

0.0

—

0.0

—

0.0

—

ns

GLB register hold time after clock, input register path

1.0

—

1.0

—

1.0

—

ns

t

HIRZ

GLB register hold time after clock, input register path with

zero hold

0.0

—

0.0

—

0.0

—

ns

t

CO

t

R

t

RW

t

PTOE/DIS

t

GPTOE/DIS

t

GOE/DIS

t

CW

GLB register clock-to-output delay

—

3.4

—

4.5

—

6.0

ns

External reset pin to output delay

—

6.3

—

9.0

—

10.5

ns

External reset pulse duration

2.0

—

4.0

—

4.0

—

ns

Input to output local product term output enable/disable

—

7.0

—

9.0

—

10.5

ns

Input to output global product term output enable/disable

—

9.0

—

10.3

—

12.0

ns

Global OE input to output enable/disable

—

5.0

—

7.0

—

8.0

ns

Global clock width, high or low

2.2

—

3.3

—

4.0

—

ns

t

GW

Global gate width low (for low transparent) or high (for

high transparent)

2.2

—

3.3

—

4.0

—

ns

t

WIR

f

MAX

f

MAX

(Ext.) Clock frequency with external feedback, [1/ (t

S

+ t

CO

)]

1. Timing numbers are based on default LVCMOS 1.8 I/O buffers. Use timing adjusters provided to calculate other standards.

2. Measured using standard switching circuit, assuming GRP loading of 1 and 1 output switching.

3. Pulse widths and clock widths less than minimum will cause unknown behavior.

4. Standard 16-bit counter using GRP feedback.

Input register clock width, high or low

2.2

—

3.3

—

4.0

—

ns

4

Clock frequency with internal feedback

227

—

168

—

125

—

MHz

156

—

111

—

86

—

MHz

Timing v.3.2

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LC4128x | 3.3V/2.5V/1.8V In-System Programmable SuperFAST High density PDLs |

| LC4256V | 3.3V/2.5V/1.8V In-System Programmable SuperFAST High density PDLs |

| LC4256x | 3.3V/2.5V/1.8V In-System Programmable SuperFAST High density PDLs |

| LC4032x | 3.3V/2.5V/1.8V In-System Programmable SuperFAST High density PDLs |

| LC4064x | 3.3V/2.5V/1.8V In-System Programmable SuperFAST High density PDLs |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LC43A | 制造商:Microsemi Corporation 功能描述:TVS SGL UNI-DIR 43V 1.5KW 2PIN DO-13 - Bulk 制造商:Microsemi Corporation 功能描述:TVS 1500V LOW CAP DO-202AA 制造商:Microsemi Corporation 功能描述:TVS DIODE 43VWM 69.4VC DO202AA 制造商:Crydom 功能描述: |

| LC45 | 制造商:Microsemi Corporation 功能描述:TVS SGL UNI-DIR 45V 1.5KW 2PIN DO-13 - Bulk 制造商:Microsemi Corporation 功能描述:TVS DIODE 45VWM 80.3VC DO202AA |

| LC4500291KB-XT | 制造商:ON Semiconductor 功能描述:LCD DISPLAY DRIVER COG - Waffle Pack |

| LC450029PKB-XT | 制造商:ON Semiconductor 功能描述:LCD DISPLAY DRIVER COG - Waffle Pack |

| LC450M0100BPF-2235 | 制造商:Yageo Corporation 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。