- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄370391 > GS9025 GENLINX II Serial Digital Receiver PDF資料下載

參數(shù)資料

| 型號(hào): | GS9025 |

| 英文描述: | GENLINX II Serial Digital Receiver |

| 中文描述: | GENLINX二串行數(shù)字接收機(jī) |

| 文件頁(yè)數(shù): | 9/30頁(yè) |

| 文件大小: | 445K |

| 代理商: | GS9025 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)當(dāng)前第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)

19922 - 2

9

G

2. FLYWHEEL BLOCK

2.1 FVH Flywheel

The flywheel

’

s primary function is to provide accurate field,

vertical, and horizontal output signals in the presence of

noisy or error prone input data. Flywheel synchronization is

based on the TRS words in the incoming data stream. The

FVH flywheel synchronizes to the incoming data stream in

less than two fields once the incoming standard has been

detected. Once synchronized, the TRS words in the

incoming data stream and those generated by the flywheel

are constantly compared to ensure that the flywheel

remains synchronized.

Noise insensitivity is accomplished by re-synchronizing the

flywheel to the data stream only if it is not aligned for long

periods of time. For component signals, four mismatches

between the EAV signal in the incoming and flywheel

generated signals over a window of eight lines will trigger

the flywheel to begin re-synchronization. For composite

signals, re-synchronization is triggered by mismatches in

the TRS encoded line numbers or field bits for 7

consecutive lines.

The flywheel can be disabled by asserting the FLYWDIS

control signal HIGH. Disabling the flywheel will remove the

effective noise immunity. In this mode, FVH values will be

decoded directly from the incoming data stream rather than

being decoded from the flywheel. Note that when the

flywheel is disabled, TRS_BLANK and TRS_INSERT will not

function correctly if enabled. Therefore if the flywheel is

disabled then so should TRS_BLANK and TRS_INSERT.

FLYWDIS is available as an input pin and as a bit in the

HOSTIF write table.

The SWITCHFLYW control signal is used in applications

where the data input to the GS9020A is switched between

two synchronous signals. In this case, the two signals may

be slightly misaligned and would normally require the

flywheel to completely re-synchronize. In this scenario, the

re-synchronization time would be undesirable. Asserting the

SWITCHFLYW bit of the HOSTIF write table HIGH allows the

flywheel to re-synchronize to the new incoming signal at the

end of the switching line.

For this functionality to operate properly, the two signals

must both be in the active picture portion of the switching

line at the time of the switch.

2.2 Accurate FVH Timing Signals

The F[2:0] signals indicate the current field of the video

data. Three F bits are necessary to accommodate the

composite PAL standard which has 8 fields. The F[2:0] bits

are available on dedicated output pins and via the HOSTIF

read table. Figure 8a and 8b illustrate the position of the

F[2:0] transition within a line for component and composite

signals, respectively. For component standards only, F0 is

used to indicate fields 0 and 1. The lines on which the

transitions occur conform to the SMPTE standards.

For component signals, the horizontal (H) signal is HIGH

during the horizontal blanking region of the output signal,

from EAV to SAV inclusive. For composite signals, the H

signal remains HIGH only for the 3FF, 000, 000, 000, and

TRSID words. Figure 8a and 8b illustrate the H output signal

timing for component and composite signals, respectively.

The vertical (V) signal timing is dependent on the incoming

video standard and the VBLANKS/L control signal. The

VBLANKS/L signal is available as an input pin and via the

HOSTIF write table and should be set to indicate the form of

the incoming data stream. This allows the flywheel to

correctly structure the V bit for flywheel synchronization,

TRS insertion, and TRS error indication.

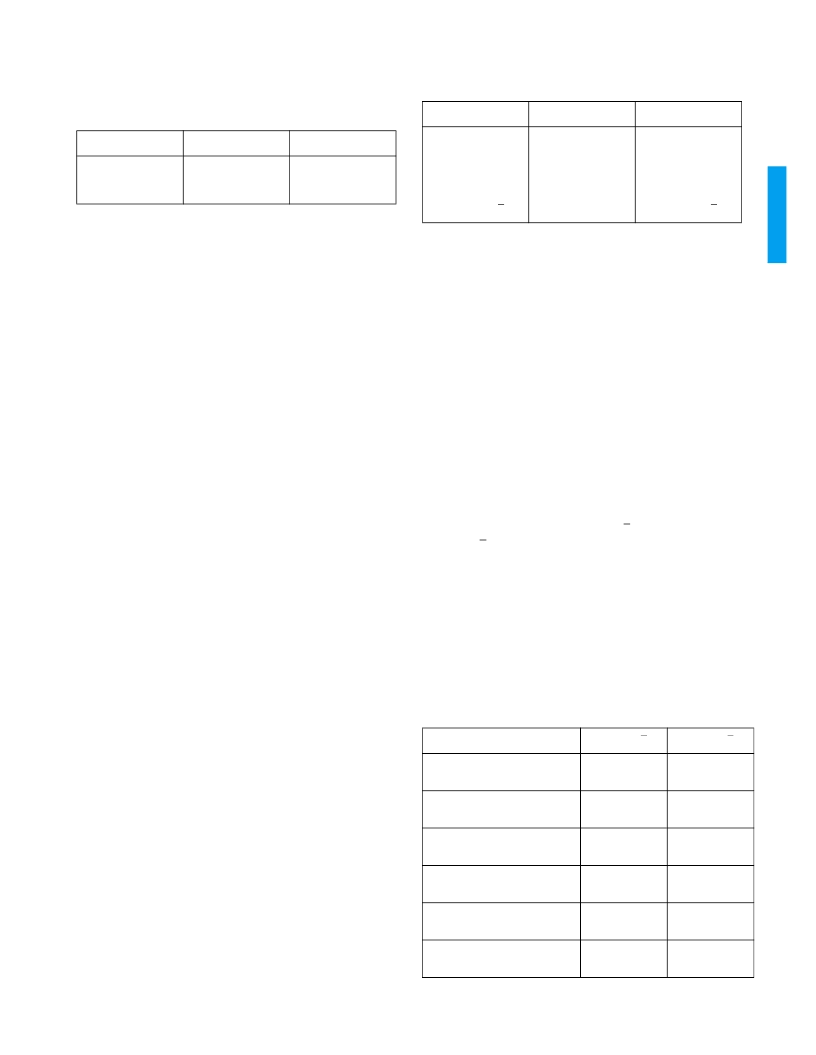

For component based standards, the transition of the V

output signal within a line is shown in Figure 8a. The line on

which the V output signal transitions from HIGH to LOW is

summarized in the table below. The lines on which the LOW

to HIGH transition occurs conform to the SMPTE standards.

PIN

LOGIC OPR

HOST BIT

FLYWDIS

OR

FLYWDIS

SWITCHFLYW

PIN

LOGIC OPR

HOST BIT

F[2:0]

F[2:0]

V

H

VBLANKS/L

AND

VBLANKS/L

STANDARD

VBLANKS/L=1

VBLANKS/L=0

NTSC 4:2:2 Component

(13.5MHz Y sampling)

9/272

19/282

NTSC 4:2:2 16x9 Widescreen

(18MHz Y sampling)

9/272

19/282

NTSC 4:4:4:4 Single Link

(13.5MHz Y sampling)

9/272

19/282

PAL 4:2:2 Component

(13.5MHz Y sampling)

22/335

22/335

PAL 4:2:2 16x9 Widescreen

(18MHz Y sampling)

22/335

22/335

PAL 4:4:4:4 Single Link

(13.5MHz Y sampling)

22/335

22/335

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| GS9032 | 143-540Mb/s Serializer for SDI and DVB-ASI. |

| GS9032-CTM | SMPTE |

| GS9032-CVM | SMPTE |

| GS9035 | GENLINX II Serial Digital Reclocker |

| GS9035C | 143-360Mb/s Reclocker. |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| GS9025 44PQFP | 制造商:Gennum Corporation 功能描述: |

| GS9025A | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:Serial Digital Receiver |

| GS9025A_05 | 制造商:GENNUM 制造商全稱(chēng):GENNUM 功能描述:Serial Digital Receiver |

| GS9025ACQM | 制造商:Rochester Electronics LLC 功能描述: 制造商:Gennum Corporation 功能描述: |

| GS9025ACQME3 | 制造商:Semtech Corporation 功能描述:Cable Equalization 44-Pin MQFP Tray 制造商:Semtech Corporation 功能描述:GS9025 Series 540 Mb/s Cable Equalization Serial Digital Receiver - MQFP-44 制造商:Semtech Corporation 功能描述:Receiver |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。