- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370391 > GS9025 GENLINX II Serial Digital Receiver PDF資料下載

參數(shù)資料

| 型號: | GS9025 |

| 英文描述: | GENLINX II Serial Digital Receiver |

| 中文描述: | GENLINX二串行數(shù)字接收機 |

| 文件頁數(shù): | 12/30頁 |

| 文件大?。?/td> | 445K |

| 代理商: | GS9025 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁當(dāng)前第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁

19922 - 2

12

G

3.4 Ancillary Checksum Verification

For each received ANC packet in the incoming data, the

device compares the calculated checksum value to the

embedded checksum for that ANC packet. If the

checksum values do not match for any ANC packets within

a field, an error is reported via the ancillary EDH flag in the

EDH packet. In addition, if the ANC_CHKSM input pin or

HOSTIF write table bit is asserted HIGH, the ancillary

checksum correction block is enabled and the checksum in

the ANC packet is replaced with the calculated one. This

update is required to prevent the ANC data error from being

flagged at every downstream EDH chip.

When implementing applications which use the EDH core

(ie. BYPASS_EDH set LOW), ANC_CHKSM will indicate a

downstream FF/AP EDH error when an illegal/non-allowed

(3FC

H

-3FF

H

) ANC_CHKSM input value is detected. As

such, these values should not be present in the incoming

data and the corresponding FF/AP EDH errors should not

occur. However, if the user wishes to disable the

ANC_CHKSM function, it can be deactivated by setting

both the ANC_CHSKM pin and the ANC_CHKSM host

interface bit LOW.

If the chip is receiving ANC EDH flag information through

the flag port or the HOSTIF, then the ANC EDH flag

generated by the ancillary checksum verification block will

be overwritten. However, the additional FF/AP EDH flag will

still appear at the next downstream chip if an illegal

checksum

of

3FC

H

-3FF

H

ANC_CHKSM function was enabled.

was

detected

and

the

If a checksum error is detected in the EDH packet itself, an

additional separate error flag, EDH_CHKSM is set HIGH in

the HOSTIF read table.

3.5 UES Error Flag Updating

In receive mode, a UES flag is set HIGH in the outgoing

EDH packet if the corresponding UES flag was HIGH in the

incoming packet or if the corresponding V bit was LOW.

(For example, if the incoming Active Picture V bit is LOW,

the outgoing Active Picture UES bit will be HIGH). If there is

no EDH packet in the incoming data, all three UES flags

(ANC, AP, FF) are set HIGH.

3.6 ANC_DATA

The ANC_DATA signal is set HIGH when an ancillary data

packet is exiting the GS9020A. This pin is asserted from the

start of the first header word through to the end of the

checksum word of the ANC packet, inclusive, as shown in

Figure 10.

3.7 NO_EDH

Some input data streams may lack the EDH packet. In such

cases, the NO_EDH output pin or HOSTIF read table bit is

asserted HIGH. If only a few fields lack the EDH packet, the

NO_EDH pin/bit will be asserted only for those fields.

In determining if the input data stream contains an EDH

packet, the GS9020A looks for two things. First the

presence of an ANC packet with the header 000 3FF 3FF

1F4 and second that the ANC header is in the right spot for

the video standard detected. The NO_EDH signal is a

logical NAND of these two cases. If either one is false, the

NO_EDH flag is set.

3.8 ERRORED FIELD COUNTER

The device has a 24 bit ERRORED FIELD COUNTER. The

counter increments by one on the occurrence of one or

more error flags in an OUTGOING EDH packet. The error

flags that can increment the counter are user-selectable

through the 16 ERROR SENSITIVITY bits in the HOSTIF

write table. The error flag SENSITIVITY bits are active LOW,

so that if a particular sensitivity bit is set LOW, the counter is

sensitive to errors of that type in the OUTGOING EDH

packet. The EDH_CHKSM sensitivity bit is active HIGH.

There are four modes of counter operation. The mode is set

through 2 bits in the HOSTIF write table, denoted CLR1 and

CLR0.

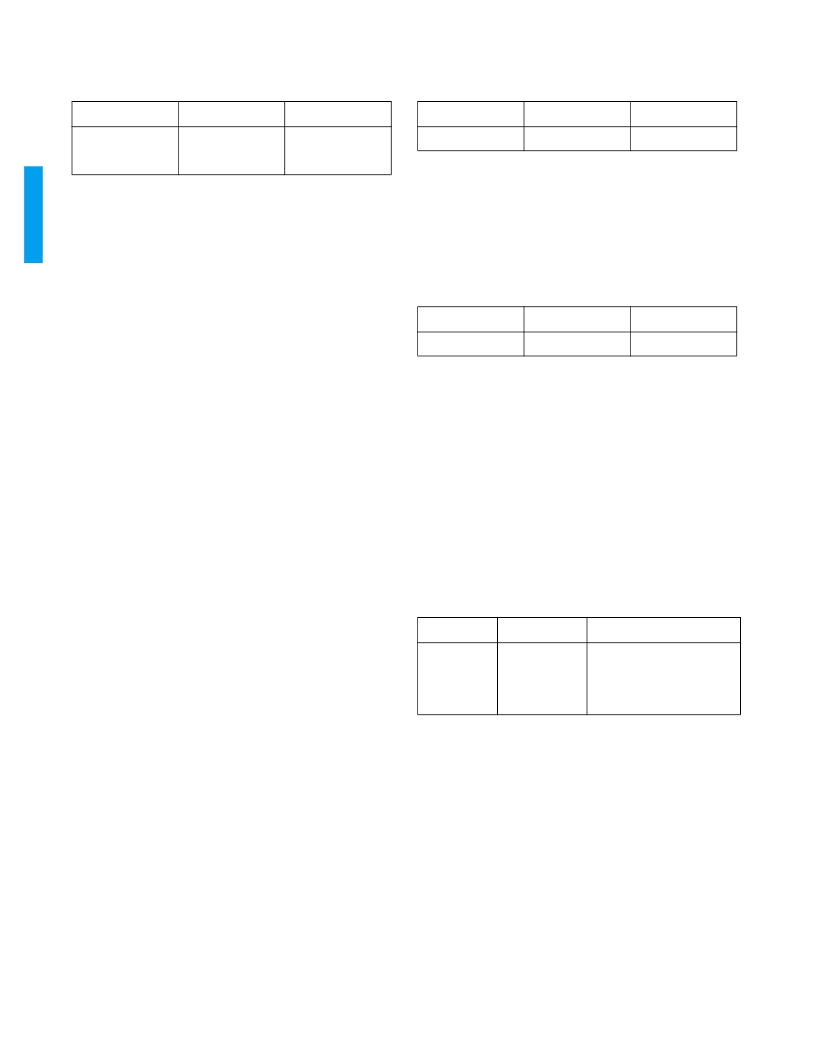

PIN

LOGIC OPR

HOST BIT

ANC_CHKSM

OR

ANC_CHKSM

EDH_CHKSM

PIN

LOGIC OPR

HOST BIT

ANC_DATA

PIN

LOGIC OPR

HOST BIT

NO_EDH

NO_EDH

PIN

LOGIC OPR

HOST BIT

ERRORED FIELD COUNTER

CLR[1:0]

ERROR SENSITIVITY BITS

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| GS9032 | 143-540Mb/s Serializer for SDI and DVB-ASI. |

| GS9032-CTM | SMPTE |

| GS9032-CVM | SMPTE |

| GS9035 | GENLINX II Serial Digital Reclocker |

| GS9035C | 143-360Mb/s Reclocker. |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| GS9025 44PQFP | 制造商:Gennum Corporation 功能描述: |

| GS9025A | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Serial Digital Receiver |

| GS9025A_05 | 制造商:GENNUM 制造商全稱:GENNUM 功能描述:Serial Digital Receiver |

| GS9025ACQM | 制造商:Rochester Electronics LLC 功能描述: 制造商:Gennum Corporation 功能描述: |

| GS9025ACQME3 | 制造商:Semtech Corporation 功能描述:Cable Equalization 44-Pin MQFP Tray 制造商:Semtech Corporation 功能描述:GS9025 Series 540 Mb/s Cable Equalization Serial Digital Receiver - MQFP-44 制造商:Semtech Corporation 功能描述:Receiver |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。