- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370391 > GS9025 GENLINX II Serial Digital Receiver PDF資料下載

參數(shù)資料

| 型號(hào): | GS9025 |

| 英文描述: | GENLINX II Serial Digital Receiver |

| 中文描述: | GENLINX二串行數(shù)字接收機(jī) |

| 文件頁(yè)數(shù): | 7/30頁(yè) |

| 文件大?。?/td> | 445K |

| 代理商: | GS9025 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)當(dāng)前第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)

19922 - 2

7

G

DETAILED DESCRIPTION

The GS9020A EDH coprocessor consists of five major

blocks:

1. Data Input/Output Block (with automatic standard

detect)

2. Flywheel Block

3. EDH Block

4. Data Processing Block

5. Host Interface (HOSTIF) Block

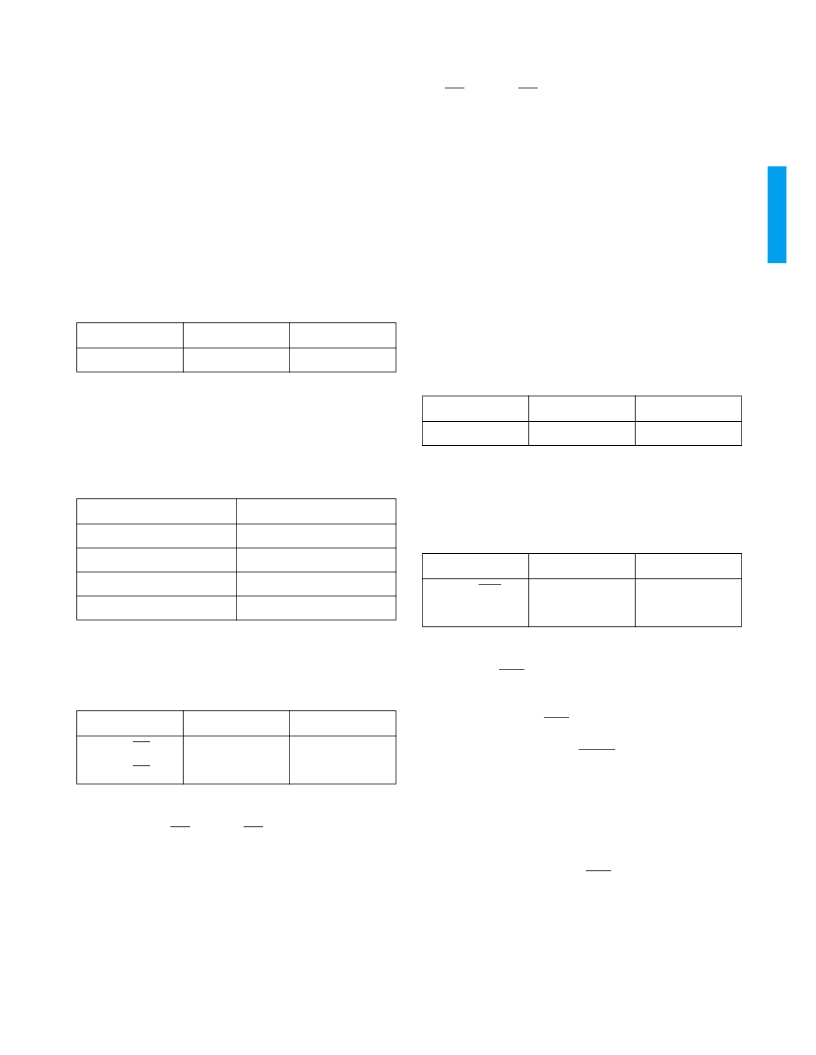

The following convention is used to differentiate device pins

from HOST interface table bits.

LOGIC OPR (logic operator) gives the combinational

relationship (if one exists), between pins which also have a

corresponding HOST bit. This operator governs the signal

the GS9020A receives. The following is the list of possible

logic operators and their meaning.

1. DATA INPUT/OUTPUT BLOCK

1.1 Serial Video Data Inputs

Serial data and clock signals are supplied to the GS9020A

chip via the SDI/SDI and SCI/SCI pins, respectively. Eight

standards are supported: Composite, 4:2:2 Component with

13.5MHz Y sampling, 4:2:2 16 x 9 wide screen with 18MHz

Y sampling, and 4:4:4:4 Component Single Link with

13.5MHz Y sampling, all in both NTSC and PAL formats.

See Table 1.

SDI/SDI and SCI/SCI are high speed Pseudo-ECL (PECL)

compatible differential inputs with internal pullup resistors

(75

nominally) as shown in Figure 4. Note that each pullup

resistor has a dedicated power pin allowing the use of other

interfacing topologies.

The internal pullup resistors allow the GS9020A to be easily

interfaced to the GS9025A as shown in Figure 5 and Figure

17. An external diode is required to offset the input signals

to the input range of the GS9020A. For maximum signal

integrity the GS9025A and GS9020A should be placed as

close together as possible.

The PECL serial input signals are first converted to CMOS

levels and then deserialized to 10 bit parallel format (based

on the TRS headers), descrambled, and then passed to the

processing core.

1.2 Parallel Digital Video Data Outputs

The output of the device is 10-bit digital video data and is

present on the DOUT[9:0] output pins.

1.3 Reserialized Data Output

The GS9020A also provides PECL differential serial data

outputs (SDO/SDO). The serial data outputs can operate in

one of two modes as controlled by the SDOMODE pin.

When SDOMODE is set LOW, re-serialized processed data

is output at the SDO/SDO output pins. In this mode it is

recommended that the lock output of the GS9025A or

GS9035A connected to the RESET input of the GS9020A,

and to a pull up resistor. This will effectively reset the

GS9020A whenever the signal lock is lost. Note that any

GS9020A programming through the host interface will be

lost after this reset. It will be necessary to reprogram the

GS9020A after each reset.

When SDOMODE is set HIGH, the serial input data is

supplied directly to the SDO/SDO output pins, bypassing

the processing core. After changing SDOMODE, the

GS9020A must be reset for proper operation.

PIN

LOGIC OPR

HOSTIF

XX

YY

LOGIC OPR

MEANING

AND

XX AND YY

OR

XX OR YY

>

XX takes precedence over YY

<

YY takes precedence over XX

PIN

LOGIC OPR

HOST BIT

SDI, SDI

SCI, SCI

PIN

LOGIC OPR

HOST BIT

DOUT[9:0]

PIN

LOGIC OPR

HOST BIT

SDO, SDO

SDOMODE

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| GS9032 | 143-540Mb/s Serializer for SDI and DVB-ASI. |

| GS9032-CTM | SMPTE |

| GS9032-CVM | SMPTE |

| GS9035 | GENLINX II Serial Digital Reclocker |

| GS9035C | 143-360Mb/s Reclocker. |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| GS9025 44PQFP | 制造商:Gennum Corporation 功能描述: |

| GS9025A | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Serial Digital Receiver |

| GS9025A_05 | 制造商:GENNUM 制造商全稱:GENNUM 功能描述:Serial Digital Receiver |

| GS9025ACQM | 制造商:Rochester Electronics LLC 功能描述: 制造商:Gennum Corporation 功能描述: |

| GS9025ACQME3 | 制造商:Semtech Corporation 功能描述:Cable Equalization 44-Pin MQFP Tray 制造商:Semtech Corporation 功能描述:GS9025 Series 540 Mb/s Cable Equalization Serial Digital Receiver - MQFP-44 制造商:Semtech Corporation 功能描述:Receiver |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。