- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370391 > GS9025 GENLINX II Serial Digital Receiver PDF資料下載

參數(shù)資料

| 型號(hào): | GS9025 |

| 英文描述: | GENLINX II Serial Digital Receiver |

| 中文描述: | GENLINX二串行數(shù)字接收機(jī) |

| 文件頁數(shù): | 14/30頁 |

| 文件大小: | 445K |

| 代理商: | GS9025 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁當(dāng)前第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁

19922 - 2

14

G

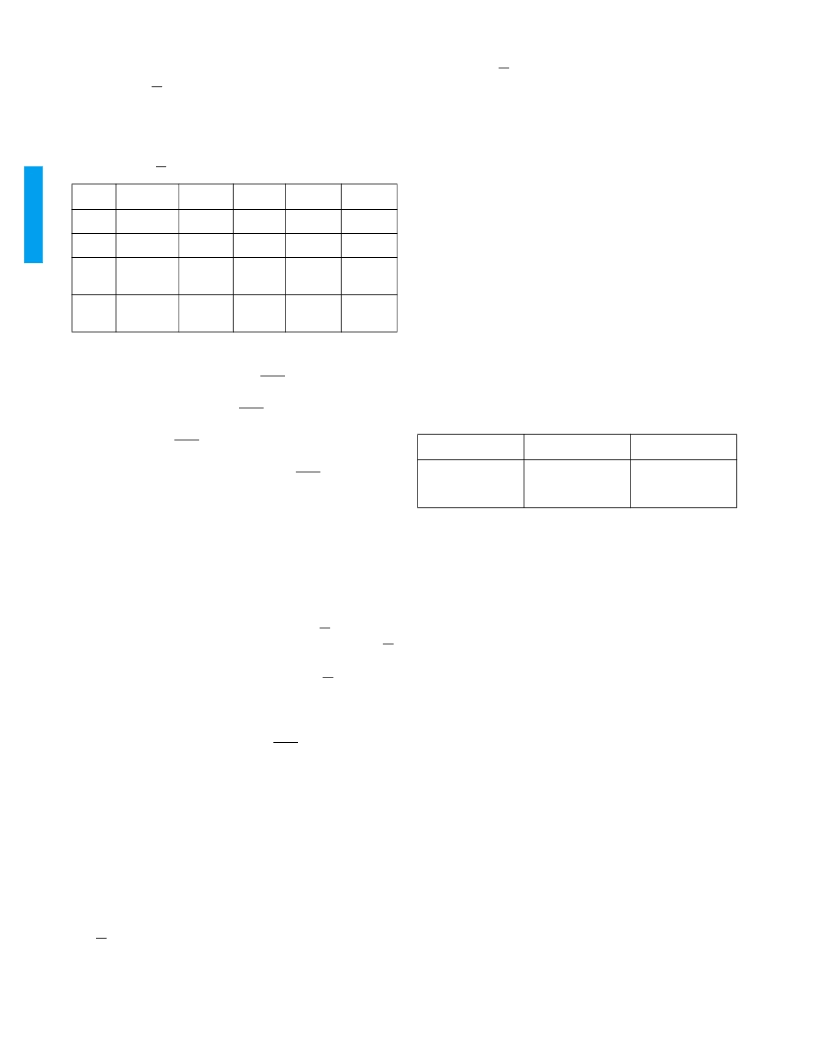

3.10.2 Read Mode

When the F_R/W pin is HIGH, the flag port is in read mode

and the FL[4:0] pins are configured as outputs. The data

present on the FL[4:0] output pins, as controlled by the

S[1:0] pins, is summarized below.

Note that the 15 error flags can be read from the incoming

or outgoing EDH packet (see IN/OUT control bit above).

However, the EDH_CHKSM flag available on pin FL4 when

S[1:0] = 11 is only valid if IN/OUT is LOW. Also, the APV

and FFV bits available on pins FL[3:2] when S[1:0] = 11 are

only valid when IN/OUT is HIGH (that is, the validity bits are

always read from the incoming EDH packet). The S bit is

available regardless of the state of the IN/OUT bit.

3.10.3 FLAG PORT Read/Write Timing

Figure 12a shows a FLAG PORT write cycle followed by a

FLAG PORT read cycle and illustrates the read/write timing

requirements. Note that the signals are not latched in

exactly on the rising edge of PLCKOUT (as described in

Note 2 of the AC electrical table), but are shown as being

latched in on the rising edge for simplicity only.

A write cycle is initiated by changing the F_R/W signal from

HIGH to LOW. The first time the device samples the F_R/W

LOW (at t

0

) it is instructed to stop driving the FL[4:0] pins.

On each subsequent clock cycle (and F_R/W LOW) the

device latches in the data present on S[1:0] and FL[4:0] (at

t

1

, t

2

, t

3

and t

4

). In this example, the S[1:0] pins begin at "00"

and are incremented each clock cycle to update all the

error flags, validity bits, and the IN/OUT control bit. Note

that if a write cycle is performed to update, say the FF error

flags (S[1:0] = 00), only the FF flags are updated, and the

others are unaffected.

A delay time, t

FDIS

, is necessary to change the FL[4:0] pins

from output mode to input mode as defined in the AC timing

table and shown in Figure 12b.

The external controller can begin to drive the FL[4:0] bus

after this delay time. A simple way to allow for this is to wait

one clock cycle before starting to drive the FL[4:0] port and

thus prevent bus contention (but set the S[1:0] inputs when

F_R/W goes LOW so that flags are not unintentionally

affected).

At t

5

, the F_R/W pin is sampled HIGH, indicating a read

operation. Also at this time, the device reads in the

information on the S[1:0] pins. Upon sampling a read

operation, the device will begin driving the FLAG PORT

after a delay, t

FEN

(see Figure 12c), with invalid data. The

requested information is output on the FL[4:0] pins on the

subsequent clock, t

6

, (plus an output delay time, see AC

timing table and Figure 3). That is, there is a one clock

latency between sampling of the S[1:0] pins and when the

corresponding output information is presented on the

FL[4:0] pins. In this example, the S[1:0] pins begin at "00"

and are incremented each clock cycle to read all the error

flags, EDH_CHKSM, validity, and S bits.

The FLAG PORT is synchronous to the internal parallel

clock and hence adequate timing for writing must be

provided as indicated in the AC timing information and

Figure 2. FLAG PORT read/write cycles, relative to the data

stream, should take place as outlined in section 5.3 (HOST

INTERFACE READ/WRITE TIMING).

3.11 CRC_MODE and FLAG_MAP Mode

A common configuration is to have an input EDH chip that

checks for errors at the input of a piece of equipment,

followed by a processing block that manipulates the data,

followed by an output EDH chip that updates the CRC

values in the EDH packet before the data exits the

equipment. Because the processing block changes the

data values, the CRC values in the EDH packet no longer

represent the data stream. The output EDH chip updates

the CRC values to correctly reflect the newly modified data.

To prevent the output EDH chip from indicating erroneous

CRC errors on each field, the GS9020A has two special

modes of operation, CRC_MODE and FLAG_MAP mode.

3.11.1 CRC_MODE

In CRC_MODE, the CRC values in the EDH packet are

updated by the chip but the error flags are preserved and

unaltered, unless they are overwritten via the HOSTIF or the

FLAG PORT. This mode should be used by the output EDH

chip to prevent the newly processed data from creating

misleading EDH errors due to CRC mismatches. The device

is placed in CRC_MODE by asserting the CRC_MODE pin

HIGH.

Read Mode, F_R/

W

= 1

S[1:0]

FL4

FL3

FL2

FL1

FL0

00

FF UES

FF IDA

FF IDH

FF EDA

FF EDH

01

AP UES

AP IDA

AP IDH

AP EDA

AP EDH

10

ANC UES

ANC

IDA

ANC

IDH

ANC

EDA

ANC

EDH

11

EDH_

CHKSUM

APV

FFV

S

PIN

LOGIC OPR

HOST BIT

CRC_MODE

FLAG_MAP

OR

FLAG_MAP

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| GS9032 | 143-540Mb/s Serializer for SDI and DVB-ASI. |

| GS9032-CTM | SMPTE |

| GS9032-CVM | SMPTE |

| GS9035 | GENLINX II Serial Digital Reclocker |

| GS9035C | 143-360Mb/s Reclocker. |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| GS9025 44PQFP | 制造商:Gennum Corporation 功能描述: |

| GS9025A | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Serial Digital Receiver |

| GS9025A_05 | 制造商:GENNUM 制造商全稱:GENNUM 功能描述:Serial Digital Receiver |

| GS9025ACQM | 制造商:Rochester Electronics LLC 功能描述: 制造商:Gennum Corporation 功能描述: |

| GS9025ACQME3 | 制造商:Semtech Corporation 功能描述:Cable Equalization 44-Pin MQFP Tray 制造商:Semtech Corporation 功能描述:GS9025 Series 540 Mb/s Cable Equalization Serial Digital Receiver - MQFP-44 制造商:Semtech Corporation 功能描述:Receiver |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。