- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄375916 > FS7VS-5 (Mitsubishi Electric Corporation) HIGH-SPEED SWITCHING USE PDF資料下載

參數(shù)資料

| 型號(hào): | FS7VS-5 |

| 廠商: | Mitsubishi Electric Corporation |

| 英文描述: | HIGH-SPEED SWITCHING USE |

| 中文描述: | 高速開(kāi)關(guān)使用 |

| 文件頁(yè)數(shù): | 49/91頁(yè) |

| 文件大小: | 488K |

| 代理商: | FS7VS-5 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)當(dāng)前第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)

PSD9XX Family

PSD935G2

48

Control

Register

Setting

Direction

Register

Setting

VM

Defined In

PSDsoft

Register

Setting

Mode

Declare

pins only

0

1= output,

0= input

MCU I/O

(Note 1)

NA

Declare pins

and logic or chip

select equations

PLD I/O

NA

NA

Data Port

(Port F)

Selected for

MCU with

non-mux bus

NA

NA

NA

Address Out

(Port E, F, G)

Declare

pins only

1

1

NA

Address In

(Port A,B,C,D,F)

Declare pins

NA

NA

NA

JTAG ISP

Declare pins

only

NA

NA

NA

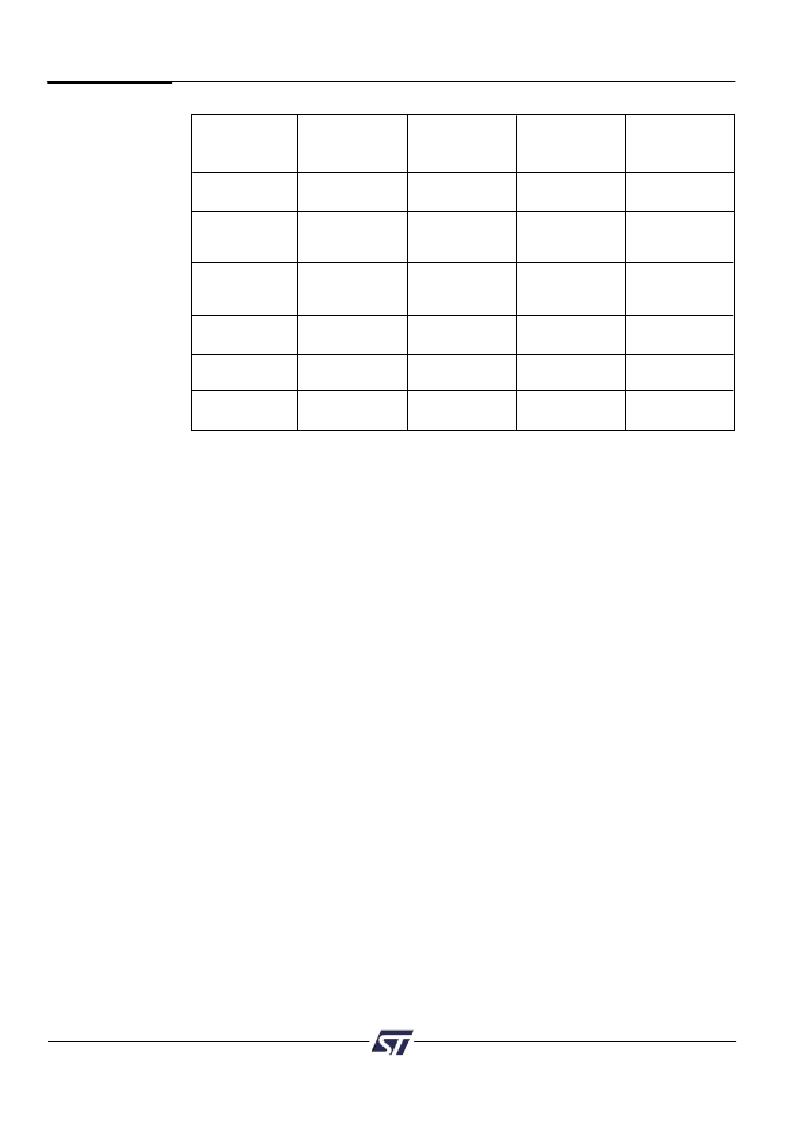

Table 17. Port Operating Mode Settings

*

NA = Not Applicable

NOTE:

1. Control Register setting is not applicable to Ports A, B and C.

9.4.2.1 MCU I/OMode

In the MCU I/O Mode, the microcontroller uses the PSD935G2 ports to expand its own

I/O ports. By setting up the CSIOP space, the ports on the PSD935G2 are mapped into the

microcontroller address space. The addresses of the ports are listed in Table 6.

A port pin can be put into MCU I/O mode by writing a ‘0’ to the corresponding bit in the

Control Register (Port E, F and G). The MCU I/O direction may be changed by writing

to the corresponding bit in the Direction Register. See the subsection on the Direction

Register in the “Port Registers” section. When the pin is configured as an output, the

content of the Data Out Register drives the pin. When configured as an input, the

microcontroller can read the port input through the Data In buffer. See Figure 20.

Ports A, B and C do not have Control Registers, and are in MCU I/O mode by default.

They can be used for PLD I/O if they are specified in PSDsoft.

9.4.2.2 PLD I/OMode

The PLD I/O Mode uses a port as an input to the CPLD’s Input Micro

Cells, and/or

as an output from the GPLD. The corresponding bit in the Direction Register must not be

set to ‘1’ if the pin is defined as a PLD input pin in PSDsoft. The PLD I/O Mode is specified

in PSDsoft by declaring the port pins, and then specifying an equation in PSDsoft.

The

PSD935G2

Functional

Blocks

(cont.)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PSD935F3V-15B81 | Configurable Memory System on a Chip for 8-Bit Microcontrollers |

| PSD935F3V-15B81I | Ceramic Chip Capacitors / MIL-PRF-55681; Capacitance [nom]: 30000uF; Working Voltage (Vdc)[max]: 100V; Capacitance Tolerance: +/-0.1pF; Dielectric: Multilayer Ceramic; Temperature Coefficient: C0G (NP0); Lead Style: Surface Mount Chip; Lead Dimensions: 0805; Termination: Solder Coated (Sn/Pb, 70/30); Body Dimensions: 0.080" x 0.050" x 0.055"; Container: Bag; Features: MIL-PRF-55681: S Failure Rate |

| PSD935F3V-15J | Configurable Memory System on a Chip for 8-Bit Microcontrollers |

| PSD935F3V-15JI | Configurable Memory System on a Chip for 8-Bit Microcontrollers |

| PSD935F3V-15M | Configurable Memory System on a Chip for 8-Bit Microcontrollers |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| FS-8000 | 制造商:FUJITSU 制造商全稱(chēng):Fujitsu Component Limited. 功能描述:MULTI-USER KVM SWITCH |

| FS-80-0-300V | 制造商:Fuji Electric 功能描述: |

| FS800R06KE3_H7E | 制造商:Infineon Technologies AG 功能描述: |

| FS800R07A2E3 | 功能描述:IGBT 模塊 IGBT Module 650V 700A RoHS:否 制造商:Infineon Technologies 產(chǎn)品:IGBT Silicon Modules 配置:Dual 集電極—發(fā)射極最大電壓 VCEO:600 V 集電極—射極飽和電壓:1.95 V 在25 C的連續(xù)集電極電流:230 A 柵極—射極漏泄電流:400 nA 功率耗散:445 W 最大工作溫度:+ 125 C 封裝 / 箱體:34MM 封裝: |

| FS800R07A2E3BOSA2 | 制造商:Infineon Technologies AG 功能描述:Trans IGBT Module N-CH 650V 700A 33-Pin |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。