- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄171235 > DSRT-L030-011 (CONEXANT SYSTEMS) SPECIALTY CONSUMER CIRCUIT, XMA PDF資料下載

參數(shù)資料

| 型號(hào): | DSRT-L030-011 |

| 廠商: | CONEXANT SYSTEMS |

| 元件分類: | 消費(fèi)家電 |

| 英文描述: | SPECIALTY CONSUMER CIRCUIT, XMA |

| 文件頁(yè)數(shù): | 76/86頁(yè) |

| 文件大小: | 667K |

| 代理商: | DSRT-L030-011 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)當(dāng)前第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)

RipTide PCI Audio/Comm Device Family Product Description

78

ROCKWELL PROPRIETARY INFORMATION

1167

+5V

VAUX

VCORE

VIO_75XX

VCORE

Fo r L ayou t:

P l a c e R 1 c l ose t o 750 1 D e v i c e .

If n o I2 S c a b l e i s p l u gg e d i n t o J 10, t hen

s h o rt J 10 p i ns 1-2, 3-4 , 5-6 us i n g sh u n ts.

No te:

In st a l l R 6 o r R 7 , n o t b o th .

R 6 I n st al l e d = V P C I P referred.

R 7 I n st al l e d = V A U X P ref erred.

#######

Controller

********

========

HHHHHH

TTTTTTT

MV_STROBE

DD3

DD5

FRAME#

PERR#

REQ#

AD12

AD3

AD17

AD16

CLO CKIN

DA[ 0. .4]

MV_SCK

DEVSEL#

ST OP#

DD1

DA1

DA2

AD20

AD27

AD11

DWR#

CBE#1

PME#

GNT#

DA3

DA4

AD26

AD5

AD30

DRD#

CBE#2

PCI RST#

DA0

DD2

V_TXSI N

CBE#3

IRDY#

INT B#

AD[ 0:31]

V_RXOUT

PCICLK

AD9

AD24

AD0

AD18

INT A#

TRDY#

SERR#

PAR

DD0

AD7

AD13

V_CTRL_SI N

AD10

AD1

AD28

DD6

AD14

DRESET#

DD[ 0. .7]

IDSEL

AD23

CBE#[ 0:3]

AD22

AD21

AD31

CBE#0

DD4

DD7

AD6

AD2

AD19

AD15

AD29

M_RXOUT

M_CTRL_SIN

M_TXSIN

AD8

AD25

AD4

JS0

JS[ 0..7]

JS7

JS5

JS4

JS3

JS6

JS2

JS1

SDATA_IN

AC_RESET#

BI T_CLK

SYNC

SDATA_OUT

I2S0DAT A

I2S0FRM

I2S0CLK

R16

10K

C52

.1uF

C159

3300pF

U5

93LC46B/SN

VDD

8

PE

6

DO

4

SK

2

PRE

7

CS

1

DI

3

GND

5

J10

1

3

5

2

4

6

D7501

U4

T QFP176P5MM

VS

S

14

VD

D

155

VS

S

33

VS

S

39

VD

D

165

VS

S

50

VS

S

62

VS

S

68

VS

S

75

VS

S

84

VS

S

13

VS

S

95

VS

S

103

VS

S

112

VS

S

121

VS

S

123

VS

S

131

VI

O

34

VS

S

141

VS

S

156

VS

S

164

VI

O

99

VD

D

49

VD

D

38

VD

D

12

SR3IN

109

VD

D

15

MRXCLK

27

SR4IN

110

VD

D

32

MRXD

28

VD

D

67

SR1234CLK

101

VD

D

61

SR3OUT

107

SR1234FRM

104

VD

D

74

MT XCLK

26

VD

D

102

VD

D

83

SR1IN

105

SR4OUT

108

VD

D

122

VD

D

111

SR2IN

106

VD

D

120

MTXD

25

CBE3#

52

VD

D

130

CBE0#

88

VD

D

142

IDSEL

53

CBE2#

64

CBE1#

77

FRAME#

65

I2S1DAT A

24

I2S1FRM

23

INT A#

29

IRDY#

66

TRDY#

69

DEVSEL#

70

I2S1CLK

22

PCI RST#

31

PCICLK

35

ST OP#

71

I2S0DAT A

21

PERR#

72

CLKRUN

40

INT B#

30

PME#

41

I2S0FRM

20

SERR#

73

PAR

76

I2S0CLK

19

GNT#

36

REQ#

37

DD0

133

DA0

119

DD1

132

AD10

85

DD2

129

DA1

118

DD3

128

DD4

127

DA2

117

DD5

126

AD28

45

DD6

125

DA3

116

DD7

124

AD12

81

DA4

115

AD9

86

AD27

46

AD8

87

AD26

47

AD25

48

AD11

82

AD24

51

AD23

54

AD7

89

AD22

55

AD6

90

AD21

56

AD5

91

AD4

92

AD3

93

AD2

96

AD1

97

AD0

98

AD20

57

AD19

58

AD18

59

AD17

60

AD16

63

AD15

78

AD14

79

AD13

80

AD31

42

AD30

43

AD29

44

SCANENB

172

SCANMODE

173

SEEPCS

137

SPEEDO

138

SEEPCLK

139

SEEPDI

140

TCK

143

TDI

144

TDO

145

TMS

146

TRST#

147

BI T_CLK

150

SDATA_IN

152

SDATA_OUT

154

SYNC

157

RESET#

158

SR8FRM

4

SR8CLK

3

SR8DU

2

SR8DD

1

JB2

11

JB1

10

JA2

18

JA1

17

JBY

16

JBX

9

JAY

8

JAX

7

MIDI_OUT

6

MI DI_I N

5

MRESET#

134

DWR#

114

DRD#

113

M_CS#

135

M_I RQ

136

GPI2/ VO L_UP

174

GPI3/VOL_DWN

175

GPI4/VOL_MUT E

176

GPIO5/ VAUXEN#

166

GPIO4/VPCIEN#

167

GPIO3/DOCKSENSE

168

GPIO2/ VPCI PREFERRED

169

GPIO1

170

GPIO0

171

GPIO6VPCIDET

163

GPIO7/VAUXDET

162

GPI1/RING WAKE#

161

GPI0/ IRING #

160

GATE_RST#

100

BIT _CLKD

151

SDATA_IND

153

RESET D#

159

MPLLOUT

148

MPLLCAP

149

VD

D

94

R1

0

SH1

SHUNT

1

SH2

SHUNT

1

SH3

SHUNT

1

R6

0

R7

0

CBE#[ 0:3]

AD[ 0:31]

DD[ 0. .7]

DA[ 0. .4]

VO L_DWN

CLO CKIN

SI _FRAME

V_RXOUT

DRESET#

DRD#

MIDI_T X

DWR#

V_TXSI N

MV_SCK

M_INT

PME#

MIDI_RX

V_CTRL_SI N

SERR#

PCICLK

REQ#

M_RX

M_RXOUT

TRDY#

INT B#

PAR

M_CS#

GNT#

SI _CLK

M_CTRL_SIN

PCI RST#

VO L_UP

IRING#

ST OP#

RI NGWAKE#

M_T XCLK

SI_RX

IDSEL

M_TXSIN

VO L_MUT E

M_RXCLK

MV_STROBE

INT A#

FRAME#

M_T X

IRDY#

DEVSEL#

PERR#

SI_TX

VPCIEN#

VAUXEN#

JS[ 0..7]

SDATA_IN

SDATA_OUT

AC_RESET#

BI T_CLK

SYNC

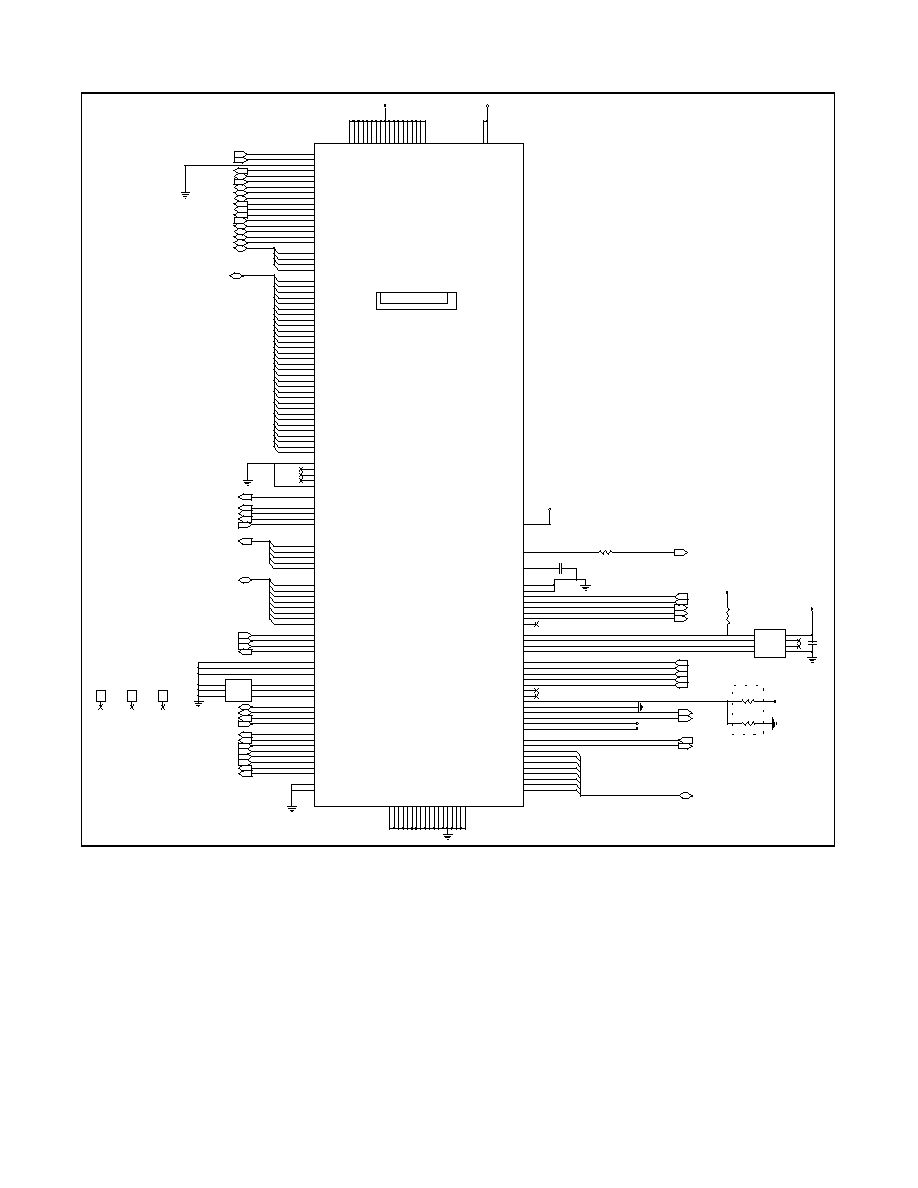

Figure 22. RipTide Reference Design Schematic P04: Controller (ACC) (176-Pin TQFP) Interface

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| DSRT-L050-011 | SPECIALTY CONSUMER CIRCUIT, XMA |

| DSS710D223S12-22 | 1 FUNCTIONS, 12 V, 7 A, DATA LINE FILTER |

| DST9HB32E101Q55J | 1 FUNCTIONS, 250 V, 6 A, DATA LINE FILTER |

| DST9HB32E220Q55J | 1 FUNCTIONS, 250 V, 6 A, DATA LINE FILTER |

| DST9HB32E222Q55J | 1 FUNCTIONS, 250 V, 6 A, DATA LINE FILTER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| DSR-TSS-S1 | 制造商:DOMINANT 制造商全稱:DOMINANT Semiconductors 功能描述:Right Angle LED |

| DSR-TSS-S2 | 制造商:DOMINANT 制造商全稱:DOMINANT Semiconductors 功能描述:Right Angle LED |

| DSR-TSS-ST2-1 | 制造商:DOMINANT 制造商全稱:DOMINANT Semiconductors 功能描述:Right Angle LED |

| DSR-TSS-T1 | 制造商:DOMINANT 制造商全稱:DOMINANT Semiconductors 功能描述:Right Angle LED |

| DSR-TSS-T2 | 制造商:DOMINANT 制造商全稱:DOMINANT Semiconductors 功能描述:Right Angle LED |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。