- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄378593 > DSP56800ERM (飛思卡爾半導(dǎo)體(中國)有限公司) 16-bit Digital Signal Controllers PDF資料下載

參數(shù)資料

| 型號: | DSP56800ERM |

| 廠商: | 飛思卡爾半導(dǎo)體(中國)有限公司 |

| 英文描述: | 16-bit Digital Signal Controllers |

| 中文描述: | 16位數(shù)字信號控制器 |

| 文件頁數(shù): | 27/124頁 |

| 文件大?。?/td> | 1880K |

| 代理商: | DSP56800ERM |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁當(dāng)前第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁

Pin Descriptions

56F8013 Technical Data, Rev. 2

Freescale Semiconductor

Preliminary

27

3.5 Pin Descriptions

3.5.1

The relaxation oscillator is included on chip and the reset mode is to use this as the clock source for the

chip. The user then has the option of switching to an external clock reference if desired.

External Reference (GPIOB6 / RXD)

Part 4 Memory Map

4.1 Introduction

The 56F8013 device is a 16-bit motor-control chip based on the 56800E core. It uses a Harvard-style

architecture with two independent memory spaces for Data and Program. On-chip RAM is used in both

spaces and Flash memory is used only in Program space.

This section provides memory maps for:

Program Address Space, including the Interrupt Vector Table

Data Address Space, including the EOnCE Memory and Peripheral Memory Maps

On-chip memory sizes for the device are summarized in

Table 4-1

.

Flash memories’ restrictions are

identified in the “Use Restrictions” column of

Table 4-1

.

4.2 Interrupt Vector Table

Table 4-2

provides the 56F8013’s reset and interrupt priority structure, including on-chip peripherals. The

table is organized with higher-priority vectors at the top and lower-priority interrupts lower in the table.

As indicated, the priority of an interrupt can be assigned to different levels, allowing some control over

interrupt priorities. All level 3 interrupts will be serviced before level 2, and so on. For a selected priority

level, the lowest vector number has the highest priority.

The location of the vector table is determined by the Vector Base Address (VBA). Please see

Section

5.6.11

for the reset value of the VBA.

By default, VBA = 0, and the reset address and COP reset address will correspond to vector 0 and 1 of the

interrupt vector table. In these instances, the first two locations in the vector table must contain branch or

JMP instructions. All other entries must contain JSR

instructions.

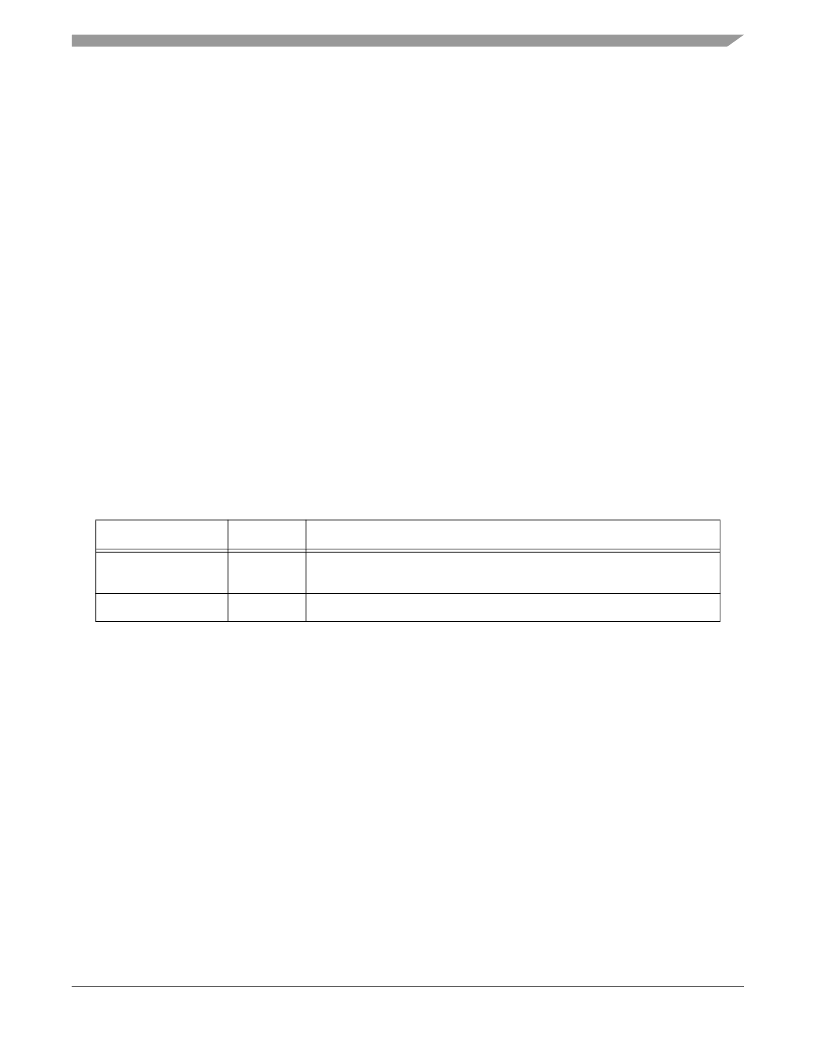

Table 4-1 Chip Memory Configurations

On-Chip Memory

56F8013

Use Restrictions

Program Flash

(PFLASH)

8k x 16

Erase / Program via Flash interface unit and word writes to CDBW

Unified RAM (ram)

2k x 16

Usable by both the Program and Data memory spaces

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| DSP56800E | Digitial Signal Controller |

| DSP56853 | Digitial Signal Controller |

| DSP56854 | Digitial Signal Controller |

| DSP56855 | Digitial Signal Controller |

| DSP56856 | Digitial Signal Controller |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| DSP56800ESDKPB | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Embedded SDK for DSP56800E Rev 2.0E. Rev 6.0 Product Brief |

| DSP56800FM | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:Preliminary Technical Data DSP56F826 16-bit Digital Signal Processor |

| DSP56800FM/D | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:DSP56824 16-Bit Digital Signal Processor |

| DSP56800FMD | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:Preliminary Technical Data DSP56F826 16-bit Digital Signal Processor |

| DSP56800SDKPB | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Embedded SDK for DSP56800 Rev 3.0. Rev 7.0 Product Brief |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。