- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄378593 > DSP56004FJ81 (飛思卡爾半導(dǎo)體(中國(guó))有限公司) SYMPHONY AUDIO DSP FAMILY 24-BIT DIGITAL SIGNAL PROCESSORS PDF資料下載

參數(shù)資料

| 型號(hào): | DSP56004FJ81 |

| 廠商: | 飛思卡爾半導(dǎo)體(中國(guó))有限公司 |

| 元件分類: | 數(shù)字信號(hào)處理 |

| 英文描述: | SYMPHONY AUDIO DSP FAMILY 24-BIT DIGITAL SIGNAL PROCESSORS |

| 中文描述: | Symphony音頻DSP系列的24位數(shù)字信號(hào)處理器 |

| 文件頁(yè)數(shù): | 56/82頁(yè) |

| 文件大?。?/td> | 636K |

| 代理商: | DSP56004FJ81 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)當(dāng)前第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)

2-32

DSP56004/D, Rev. 3

For More Information On This Product,

Go to: www.freescale.com

MOTOROLA

Specifications

Serial Host Interface (SHI) I

2

C Protocol Timing

Example:

for C

L

= 50 pF, R

P

= 2 k

, f = 88 MHz, Bypassed Filter mode: The master,

when operating with a DSP56004 SHI I

2

C slave with an 88 MHz operating frequency,

must generate a bus free time greater than 36 ns (T172 slave). Thus, the minimum

permissible t

I

This implies a maximum I

2

C serial frequency of 1010 kHz.

2

CCP

is 56

×

T

C

which gives a bus free time of at least 41 ns (T172 master).

In general, bus performance may be calculated from the C

L

and R

P

of the bus, the

Input Filter modes and operating frequencies of the master and the slave.

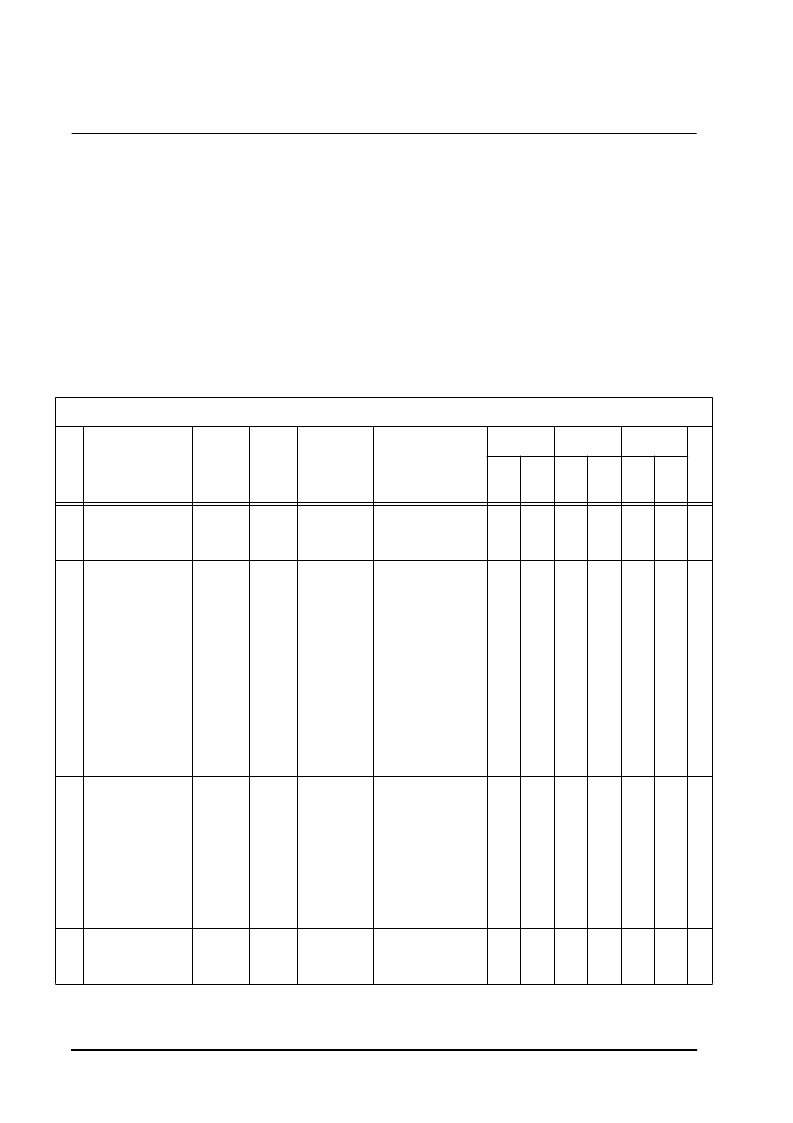

Table 2-15

contains the expressions required to calculate all relevant performance timing for a

given C

L

and R

P

.

Table 2-15

SHI Improved I

2

C Protocol Timing

Improved I

2

C (C

L

= 50 pF, R

P

= 2 k

)

No.

Char.

Sym.

Mode

Filter

Mode

Expression

50 MHz

2

66 MHz

3

81 MHz

4

U

n

i

t

Min Max Min Max Min Max

— Tolerable Spike

Width on SCL or

SDA

bypassed

narrow

wide

0

20

100

—

—

—

0

20

100

—

—

—

0

20

100

—

—

—

0

20

100

ns

ns

ns

171 SCL Serial Clock

Cycle

t

SCL

master

slave

bypassed

narrow

wide

bypassed

narrow

wide

t

I

2

CCP

+ 3

×

T

C

+72

+t

r

2

CCP

+ 3

×

T

C

+

245 + t

r

t

I

535 + t

r

4

×

T

C

+ T

H

+

172 + t

r

4

×

T

C

+ T

H

+

366 + t

r

4

×

T

C

+ T

H

+

648 + t

r

0.5

×

t

I

42 – t

r

0.5

×

t

I

42 – t

r

0.5

×

t

I

42 – t

r

2

×

T

C

+ 11

2

×

T

C

+ 35

2

×

T

C

+ 70

12

50

150

t

I

2

CCP

+ 3

×

T

C

+

1050

1263

1593

500

694

976

—

—

—

—

—

—

1007

1225

1591

478

672

954

—

—

—

—

—

—

989

1212

1576

466

660

942

—

—

—

—

—

—

ns

ns

ns

ns

ns

ns

172 Bus Free Time

t

BUF

master

slave

bypassed

narrow

wide

bypassed

narrow

wide

2

CCP

–

2

CCP

–

2

CCP

–

60

80

100

51

75

110

—

—

—

—

—

—

46

68

102

41

65

100

—

—

—

—

—

—

41.1

65.8

103

35.7

59.7

94.7

—

—

—

—

—

—

ns

ns

ns

ns

ns

ns

173 Start Condition

Set-up Time

t

SU;STA

slave

bypassed

narrow

wide

12

50

150

—

—

—

12

50

150

—

—

—

12

50

150

—

—

—

ns

ns

ns

F

Freescale Semiconductor, Inc.

n

.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| DSP56004ROM | SYMPHONY AUDIO DSP FAMILY 24-BIT DIGITAL SIGNAL PROCESSORS |

| DSP56721 | SymphonyTM DSP56720 / DSP56721 Multi-Core Audio Processors |

| DSPA56720AG | SymphonyTM DSP56720 / DSP56721 Multi-Core Audio Processors |

| DSPA56721AF | SymphonyTM DSP56720 / DSP56721 Multi-Core Audio Processors |

| DSPA56721AG | SymphonyTM DSP56720 / DSP56721 Multi-Core Audio Processors |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| DSP56004ROM | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:SYMPHONY AUDIO DSP FAMILY 24-BIT DIGITAL SIGNAL PROCESSORS |

| DSP56004UM | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:DSP56004 24-Bit Digital Signal Processor User's Manual Revision 1 |

| DSP56004UM/AD | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:SYMPHONY AUDIO DSP FAMILY 24-BIT DIGITAL SIGNAL PROCESSORS |

| DSP56005DS | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:DSP56005 24-Bit Digital Signal Processor Datasheet |

| DSP56005UM | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:DSP56005 24-Bit Digital Signal Processor User's Manual |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。