- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄378593 > DSP56004FJ81 (飛思卡爾半導(dǎo)體(中國)有限公司) SYMPHONY AUDIO DSP FAMILY 24-BIT DIGITAL SIGNAL PROCESSORS PDF資料下載

參數(shù)資料

| 型號: | DSP56004FJ81 |

| 廠商: | 飛思卡爾半導(dǎo)體(中國)有限公司 |

| 元件分類: | 數(shù)字信號處理 |

| 英文描述: | SYMPHONY AUDIO DSP FAMILY 24-BIT DIGITAL SIGNAL PROCESSORS |

| 中文描述: | Symphony音頻DSP系列的24位數(shù)字信號處理器 |

| 文件頁數(shù): | 17/82頁 |

| 文件大小: | 636K |

| 代理商: | DSP56004FJ81 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁當(dāng)前第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁

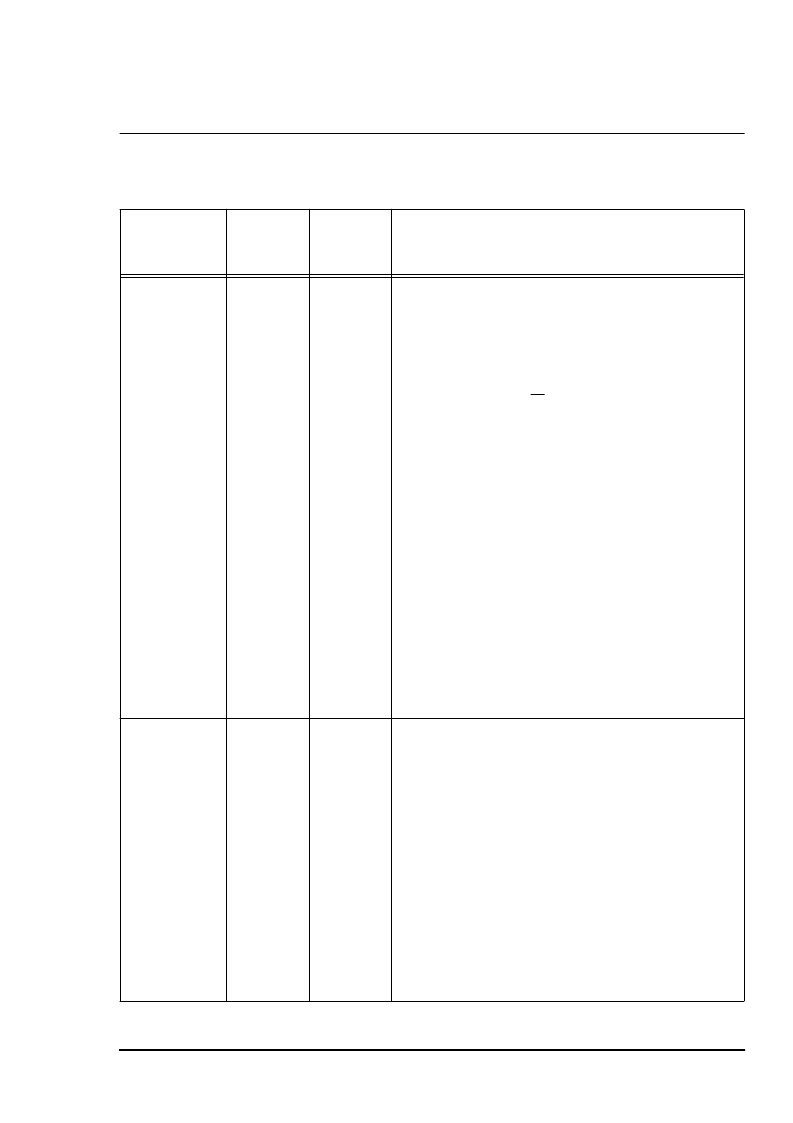

Signal/Connection Descriptions

Serial Host Interface (SHI)

MOTOROLA

DSP56004/D, Rev. 3

1-11

MISO

SDA

Input or

Output

Input or

Output

Tri-stated

SPI Master-In-Slave-Out (MISO)

—When the SPI is

configured as a master, MISO is the master data input

line. The MISO signal is used in conjunction with the

MOSI signal for transmitting and receiving serial data.

This signal is a Schmitt-trigger input when configured

for the SPI Master mode, an output when configured for

the SPI Slave mode, and tri-stated if configured for the

SPI Slave mode when SS is deasserted.

I

2

C Serial Data and Acknowledge (SDA)

—In I

2

C mode,

SDA is a Schmitt-trigger input when receiving and an

open-drain output when transmitting. SDA should be

connected to V

CC

through a pull-up resistor. SDA carries

the data for I

2

C transactions. The data in SDA must be

stable during the high period of SCL. The data in SDA is

only allowed to change when SCL is low. When the bus

is free, SDA is high. The SDA line is only allowed to

change during the time SCL is high in the case of Start

and Stop events. A high-to-low transition of the SDA line

while SCL is high is an unique situation, and is defined

as the Start event. A low-to-high transition of SDA while

SCL is high is an unique situation, and is defined as the

Stop event.

Note:

This line is tri-stated during hardware reset, software

reset, or individual reset (no need for external pull-up

in this state).

MOSI

HA0

Input or

Output

Input

Tri-stated

SPI Master-Out-Slave-In (MOSI)

—When the SPI is

configured as a master, MOSI is the master data output

line. The MOSI signal is used in conjunction with the

MISO signal for transmitting and receiving serial data.

MOSI is the slave data input line when the SPI is

configured as a slave. This signal is a Schmitt-trigger

input when configured for the SPI Slave mode.

I

2

C Slave Address 0 (HA0)—

This signal uses a Schmitt-

trigger input when configured for the I

2

C mode. When

configured for I

2

C Slave mode, the HA0 signal is used to

form the slave device address. HA0 is ignored when the

SHI is configured for the I

2

C Master mode.

Note:

This signal is tri-stated during hardware reset,

software reset, or individual reset (no need for

external pull-up in this state).

Table 1-8

Serial Host Interface (SHI) signals (Continued)

Signal Name

Signal

Type

State

during

Reset

Signal Description

F

Freescale Semiconductor, Inc.

For More Information On This Product,

Go to: www.freescale.com

n

.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| DSP56004ROM | SYMPHONY AUDIO DSP FAMILY 24-BIT DIGITAL SIGNAL PROCESSORS |

| DSP56721 | SymphonyTM DSP56720 / DSP56721 Multi-Core Audio Processors |

| DSPA56720AG | SymphonyTM DSP56720 / DSP56721 Multi-Core Audio Processors |

| DSPA56721AF | SymphonyTM DSP56720 / DSP56721 Multi-Core Audio Processors |

| DSPA56721AG | SymphonyTM DSP56720 / DSP56721 Multi-Core Audio Processors |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| DSP56004ROM | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:SYMPHONY AUDIO DSP FAMILY 24-BIT DIGITAL SIGNAL PROCESSORS |

| DSP56004UM | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:DSP56004 24-Bit Digital Signal Processor User's Manual Revision 1 |

| DSP56004UM/AD | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:SYMPHONY AUDIO DSP FAMILY 24-BIT DIGITAL SIGNAL PROCESSORS |

| DSP56005DS | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:DSP56005 24-Bit Digital Signal Processor Datasheet |

| DSP56005UM | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:DSP56005 24-Bit Digital Signal Processor User's Manual |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。