- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄376802 > DM9102 (Electronic Theatre Controls, Inc.) Single Chip Fast Ethernet NIC controller PDF資料下載

參數(shù)資料

| 型號(hào): | DM9102 |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | Single Chip Fast Ethernet NIC controller |

| 中文描述: | 單芯片快速以太網(wǎng)網(wǎng)卡控制器 |

| 文件頁(yè)數(shù): | 54/77頁(yè) |

| 文件大?。?/td> | 459K |

| 代理商: | DM9102 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)當(dāng)前第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)

DM9102A

Single Chip Fast Ethernet NIC controller

can accept the host commands to start operation. The

general procedure for initialization is described below:

(1) Read/write suitable values for the PCI configuration

registers.

each descriptor list.

(3) Write CR0 to set global host bus operation parameters.

(4) Write CR7 to mask causes of unnecessary interrupt.

(5) Write CR6 to set global parameters and start both

receive and transmit processes. Receive and transmit

processes will enter the running state and attempt to acquire

descriptors from the respective descriptor lists.

(6) Wait for any interrupt.

54

Final

Version: DM9102A-DS-F03

August 28, 2000

Data Buffer Processing Algorithm

The data buffer process algorithm is based on the

cooperation of the host and the DM9102A. The host sets

CR3 (receive descriptor base address) and CR4 (transmit

descriptor base address) for the descriptor list initialization.

The DM9102A will start the data buffer transfer after the

descriptor polling and get the ownership. For detailed

processing procedure, please see below.

1. Receive Data Buffer Processing

The DM9102A always attempts to acquire an extra

descriptor in anticipation of the incoming frames. Any

incoming frame size covers a few buffer regions and

descriptors. The following conditions satisfy the descriptor

acquisition attempt:

When start/stop receive sets immediately after being placed

in the running state.

When the DM9102A begins writing frame data to a data

buffer pointed to by the current descriptor and the buffer

ends before the frame ends.

When the DM9102A completes the reception of a frame

and the current receiving descriptor is closed.

When receive process is suspended due to no free buffer for

the DM9102A and a new frame is received.

When receive polling demand is issued. After acquiring the

free descriptor, the DM9102A processes the incoming frame

and places it in the acquired descriptor's data buffer. When

whole the received frame data has been transferred, the

DM9102A will write the status information to the last

descriptor. The same process will repeat until it encounters a

descriptor flagged as being owned by the host. If this occurs,

receive process enters the suspended state and waits the

host to service.

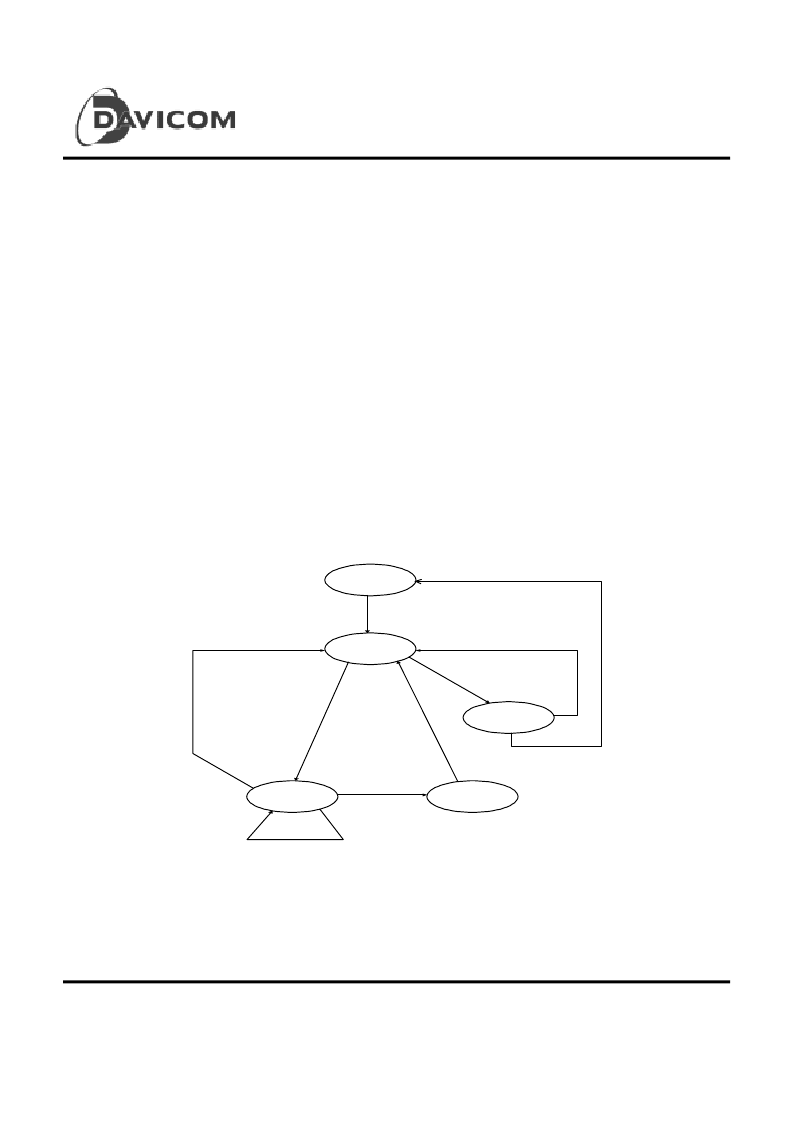

Receive Buffer Management State Transition

Stop

State

Descriptor

Access

Datat

Transfer

Write

Status

Suspended

Start Receive Command Or

Receive Poll Command

Buffer Available

( OWN bit = 1 )

FIFO Threshold

Reached

Frame Fully

Received

Buffer not

Full

Receive Buffer

Unavailable

New Frame Coming Or

Receive Poll Command

Stop Receive Command or

Reset Command

Buffer Full

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| DM9102A | Single Chip Fast Ethernet NIC controller |

| DM9102AF | Single Chip Fast Ethernet NIC controller |

| DM9102AT | Single Chip Fast Ethernet NIC controller |

| DM9108APPLICATIONENGINEERINGNOTESONE | DM9108 Application Engineering notes one |

| DM9108APPLICATIONENGINEERINGNOTESTHREE | DM9108 Application Engineering notes three |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| DM9102A | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Single Chip Fast Ethernet NIC controller |

| DM9102AF | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Single Chip Fast Ethernet NIC controller |

| DM9102AT | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Single Chip Fast Ethernet NIC controller |

| DM9102D | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:SINGLE CHIP FAST ETHEMET NIC CONTROLLER |

| DM9102DE | 制造商:DAVICOM 制造商全稱:DAVICOM 功能描述:Single Chip Fast Ethernet NIC Controller |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。