- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376802 > DM9102 (Electronic Theatre Controls, Inc.) Single Chip Fast Ethernet NIC controller PDF資料下載

參數(shù)資料

| 型號: | DM9102 |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | Single Chip Fast Ethernet NIC controller |

| 中文描述: | 單芯片快速以太網(wǎng)網(wǎng)卡控制器 |

| 文件頁數(shù): | 46/77頁 |

| 文件大小: | 459K |

| 代理商: | DM9102 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁當(dāng)前第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁

DM9102A

Single Chip Fast Ethernet NIC controller

1=100BASE-TX Half Duplex supported by the link partner

0=100BASE-TX Half Duplex not supported by the link partner

5.6

10_FDX

0, RO

10BASE-T Full Duplex Support:

1=10BASE-T Full Duplex supported by the link partner 0=10BASE-T Full

Duplex not supported by the link partner

5.5

10_HDX

0, RO

10BASE-T Support:

1=10BASE-T Half Duplex supported by the link partner

0=10BASE-T Half Duplex not supported by the link partner

5.4-5.0

Selector

<00000>,

RO

Link partner’s binary encoded protocol selector

46

Final

Version: DM9102A-DS-F03

August 28, 2000

Protocol Selection Bits:

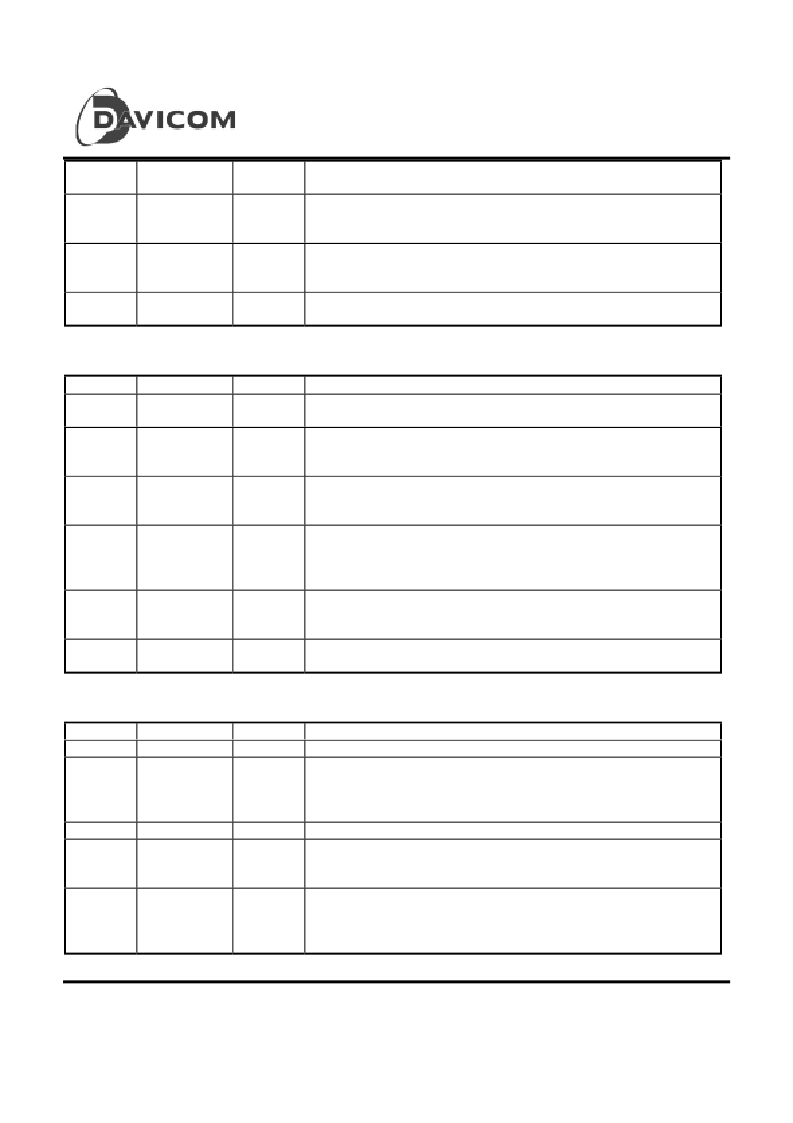

Auto-Negotiation Expansion Register (ANER) – 6

Bit

Name

Reserved

Default

0, RO

Description

6.15-6.5

Reserved:

Write as 0, ignore on read

0, RO/LH Local Device Parallel Detection Fault:

PDF=1: A fault detected via parallel detection function.

PDF=0: No fault detected via parallel detection function

0, RO

Link Partner Next Page Able:

LP_NP_ABLE=1: Link partner, next page available

LP_NP_ABLE=0: Link partner, no next page

0,RO/P

Local Device Next Page Able:

NP_ABLE=1: DM9102A, next page available

NP_ABLE=0: DM9102A, no next page

DM9102A does not support this function, so this bit is always 0.

0, RO/LH New Page Received:

A new link code word page received. This bit will be automatically

cleared when the register (Register 6) is read by management

0, RO

Link Partner Auto-negotiation Able:

A “1” in this bit indicates that the link partner supports Auto-negotiation.

6.4

PDF

6.3

LP_NP_ABLE

6.2

NP_ABLE

6.1

PAGE_RX

6.0

LP_AN_ABLE

DAVICOM Specified Configuration Register (DSCR) - 10h

Bit

Name

Reserved

F_LINK_100

Default

0, RO

0, RW

Description

16.15:16.8

16.7

Reserved

Force Good Link in 100Mbps:

0 = Normal 100Mbps operation

1 = Force 100Mbps good link status

This bit is useful for diagnostic purposes.

Reserved

Reset State Machine:

When writes 1 to this bit, all state machines of PHY will be reset. This bit is

self-clear after reset is completed.

MF Preamble Suppression Control:

MII frame preamble suppression control bit

1 = MF preamble suppression bit on

0 = MF preamble suppression bit off

16.6:16.4

16.3

Reserved

SMRST

0,RO

0,RW

16.2

MFPSC

0,RW

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| DM9102A | Single Chip Fast Ethernet NIC controller |

| DM9102AF | Single Chip Fast Ethernet NIC controller |

| DM9102AT | Single Chip Fast Ethernet NIC controller |

| DM9108APPLICATIONENGINEERINGNOTESONE | DM9108 Application Engineering notes one |

| DM9108APPLICATIONENGINEERINGNOTESTHREE | DM9108 Application Engineering notes three |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| DM9102A | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Single Chip Fast Ethernet NIC controller |

| DM9102AF | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Single Chip Fast Ethernet NIC controller |

| DM9102AT | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Single Chip Fast Ethernet NIC controller |

| DM9102D | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:SINGLE CHIP FAST ETHEMET NIC CONTROLLER |

| DM9102DE | 制造商:DAVICOM 制造商全稱:DAVICOM 功能描述:Single Chip Fast Ethernet NIC Controller |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。